请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CC2651R3SIPA 您好!

我有两个通过 SPI 进行通信的组件。 CC2651R3SIPA 是主设备。

- IMU IC -从设备

- 闪存-从器件

我的配置是"多子节点配置"。 因此、MOSI、MISO 和 SCLK 线路是共享的、并且我有两条不同的 CS 线路用于 IMU 和闪存。

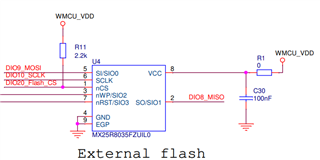

我研究了 LP-CC2651r3sipa 的原理图、发现使用了2.2K 上拉电阻器。

我知道、1k 到10k 之间的值可以很好地调节上拉电阻。 一个简单的计算表明、当 CS 为低电平时;通信期间、1.5mA 将被上拉灌入。 10k 可以将其降低至0.33 mA。

我有以下问题:

- SPI 在推挽状态下不需要上拉电阻、那么我们为什么需要使用这里的上拉电阻呢?

- 为什么2.2k 为什么不是一个更大的值?

- 为什么 未使用 CS 的内部上拉电阻、而是使用了外部电阻器-在这种情况下、引脚灌电流应该小得多?

- 如果我们有多个从器件、是否也需要 MISO 上拉?

请提供一些建议、

谢谢。