主题中讨论的其他器件: AFE7900EVM

工具与软件:

您好!

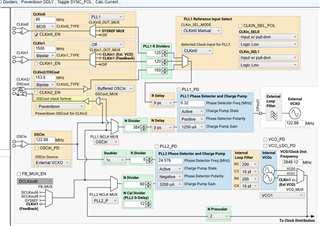

我有一个采用 LMK04828的设计、 我试图将 PLL1锁定到连接到 CLKin0的40MHz TCXO 源、但 PLL1似乎无法锁定。

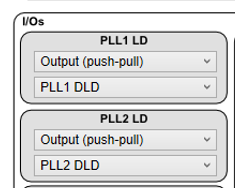

我将 PLL1 LD 配置为"PLL1 DLD"、然后 它闪烁 另一方面、我 将 PLL2 LD 配置为"PLL2 DLD"、然后将其配置为"PLL2 DLD" 保持明亮 .

以下是 PLL 的配置:

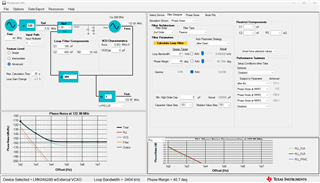

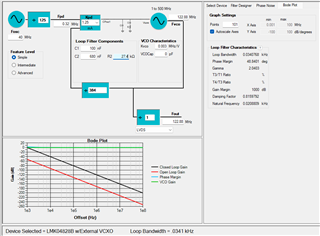

我怀疑了环路滤波器、但我在 PLLatinum 上进行了仿真、相位裕度看起来不错(40.7394°)。 我还尝试了优化方法、将电阻器替换为27.4kΩ 1而不是39kΩ(相位裕度约为48.8°)、但仍然未锁定。

我还附加来自 TICS 的配置文件:

e2e.ti.com/.../Internal-CLK5_5F00_WITHSYSREF_5F00_PLL.tcse2e.ti.com/.../HexRegisterValues4_5F00_WithSysRef_5F00_WithPLL1.txt