Thread 中讨论的其他器件:DP83869HM、 LMK05318B、 LMK5B12204

工具/软件:

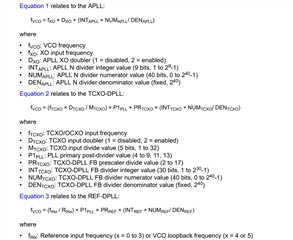

DP83869HM 的恢复时钟为25MHz、AM263所需的时钟也为25MHz。 我还想使用25MHz TCXO。 将 PLL 配置为增益为1的理想方法是什么。 很多变量似乎是影响输入频率和输出频率之间的关系的因素

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

DP83869HM 的恢复时钟为25MHz、AM263所需的时钟也为25MHz。 我还想使用25MHz TCXO。 将 PLL 配置为增益为1的理想方法是什么。 很多变量似乎是影响输入频率和输出频率之间的关系的因素

尊敬的 Shivani:

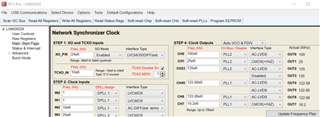

我建议使用 TICS Pro GUI 配置所有寄存器设置。 这有助于简化该过程。 GUI 根据输入的频率计划计算最优 PLL 分频器设置。

下载链接位于: https://www.ti.com/tool/TICSPRO-SW

如果您仍对 GUI 设置有疑问、敬请告知。

此致、

Jennifer

尊敬的 Shivani:

如果您仍有疑问、请告诉我!

此致、

Jennifer

LMK05028似乎不是 PLLatinum Sim 的配套产品: https://www.ti.com/tool/PLLATINUMSIM-SW#downloads