请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK05028 Thread 中讨论的其他器件: LMK05318B、 LMK5B12204

工具/软件:

我希望使用 LMK05028。 3个输出将使用 LVCMOS 时钟、一个输出将使用 LVDS 输出时钟。 我们还将使用2个 LVCMOS 时钟和1个 LVDS 时钟驱动 PLL。

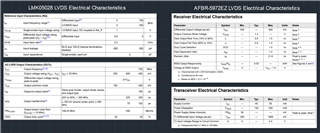

对于 LVDS 连接、VDDOx 是否会影响 LVDS 信号的电气特性? 我要连接以下2个组件。 我想确保了解 LVDS 信号的 Vpp 和 Vcm。 我为 VDDAx 引脚提供3.3V 电压、但不希望 Vpp 如此高。

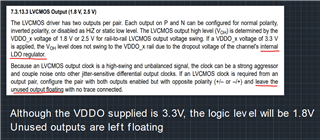

同样、为 LVCMOS 引脚提供3.3V 电压。 我的理解是内部 LDO 将输出到1.8V 逻辑电平。 LDO 可以处理我所有 LVCMOS 通道的3.3V 输入吗?