Thread 中讨论的其他器件: USB2ANY、 LMK05318、 LMK5B33216

工具/软件:

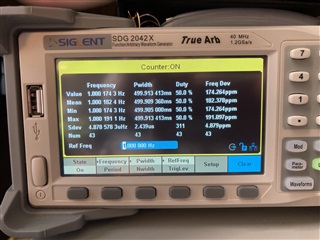

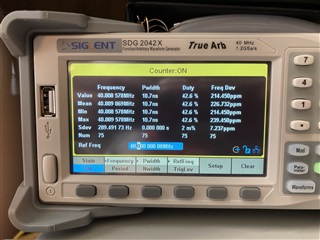

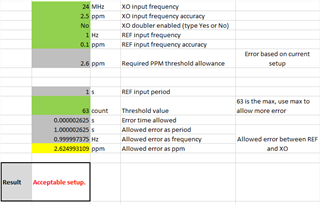

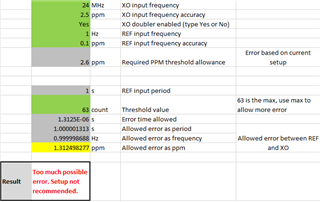

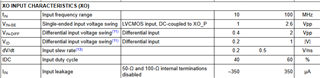

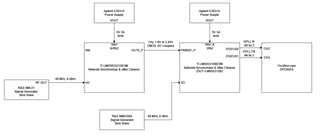

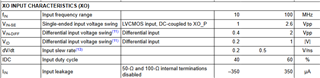

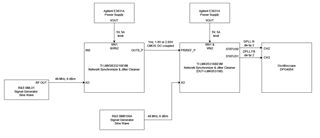

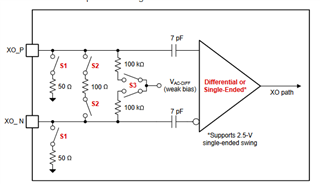

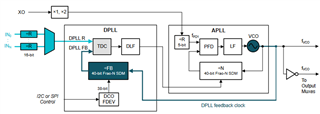

我们实施了 LMK05318B 以在数字载板中使用、从而为 RFIC 和 FPGA 提供一组参考40 MHz 信号。 我们使用一个精度为+/-2.5ppm 的24 MHz XO 和一个来自 u-blox 的 GPS 接收器来提供 PPS 输入。

我附加了 TCS 文件: https://drive.google.com/file/d/1yKAOyZ3CsoECdfFrOq-e86CL_EgNNyhQ/view?usp=drive_link

和载板原理图页面: https://drive.google.com/file/d/1t9dCRsU3_SJ7NDb1n1_-0KC1_oprw6b2/view?usp=sharing

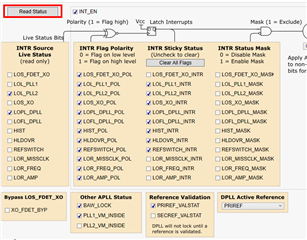

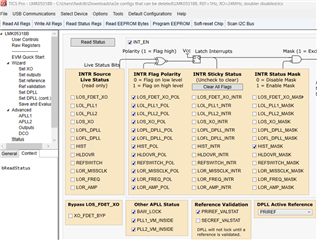

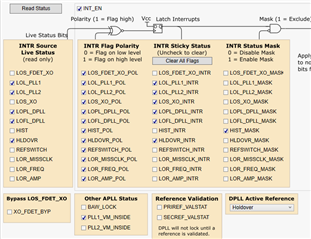

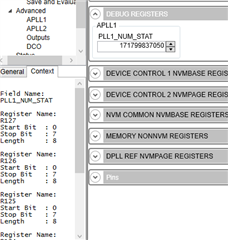

刷写 LMK 芯片时、我们有以下状态位:

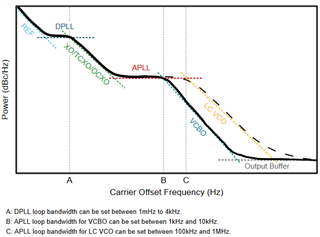

- 'LOL_PLL1':1.

- "LOL_PLL2":1.

- 'LOS_FDET_XO':0

- LOS_XO':0

- 'Hist':0

- 'HLDOVR':1.

- 'LOFL_DPLL':1.

- 'LOPL_DPLL':1.

- 'LOR_AMP':0

- 'LOR_FREQ':0

- 'LOR_MISSCLK':0

- "REFSWITCH":0

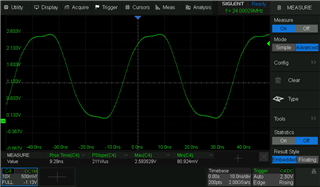

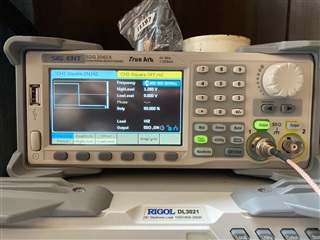

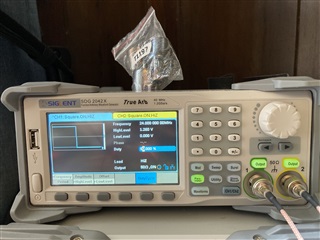

这意味着我们的 LMK 芯片的 DPLL 无法锁定、即使在等待几小时(~12小时)后也是如此。 我们已经使用示波器测量了 Pps 信号和 XO 输入、它们是有效信号。 LDO 电源工作正常。

要实现的任何输入和建议 DPLL 锁定 或采取进一步的调试步骤。