Thread 中讨论的其他器件: LMK05318、 LMK05318BEVM

工具/软件:

我们计划在我们的设计中使用 LMK5B12204网络同步器、以同步两个输出。 在对板进行原型设计之前、我们将尝试使用 LMK05318BEVM 测试器件的运行情况。 我们认为这两个芯片之间的唯一区别是 LMK05318具有8个输出、而 LMK5B12204具有4个输出。

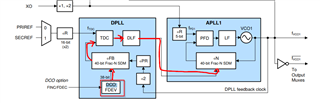

在测试时、我们尝试利用 DCO 参数来同步两个不同 EVM 的输出。 但我们注意到在某个调整值时、芯片会失去 DPLL 锁定。 我们正在努力了解为什么会发生这种情况。 在我看来、DCO 似乎会导致 BAW VCO1频率发生轻微变化。 该频率限制在 2499.750 MHz 到2500.250 MHz 之间。 因此、任何将 VCO1置于该范围之外的 DCO 校正都是无效/不允许的。 这是正确的想法吗? 如果没有、那么最大 DCO 调整的其他因素是什么?

此外、您能否说明 DCO 如何影响输出频率? 这种调整是会改变 APLL1中小数 N 分频器的分子还是会改变其他分子?

如果您需要任何其他信息、请告诉我、并提前感谢您的帮助!