工具/软件:

您好团队:

我想仔细检查时钟分配设置。

我有单个 100MHz LVDS 时钟、需要扇出到多个 PCIe 设备(SSD,控制器等)。

-

基准输入: CLKin0、由 100MHz LVDS 信号馈送

-

输出: 四个通道、每个通道都配置为 LVDS

数据表列出了 1GHz 的最低 LVDS 频率 — 您能否确认它是否适用于此用例? 此外、您能否确认该器件只需通过输入频率、从 100MHz 输入提供四个 100MHz 输出?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好团队:

我想仔细检查时钟分配设置。

我有单个 100MHz LVDS 时钟、需要扇出到多个 PCIe 设备(SSD,控制器等)。

基准输入: CLKin0、由 100MHz LVDS 信号馈送

输出: 四个通道、每个通道都配置为 LVDS

数据表列出了 1GHz 的最低 LVDS 频率 — 您能否确认它是否适用于此用例? 此外、您能否确认该器件只需通过输入频率、从 100MHz 输入提供四个 100MHz 输出?

谢谢!

尊敬的 Erdem:

我查看了您的原理图、您已经适当地配置了器件、以便向 CLKin0 输入 LVDS 信号并输出 LVDS 信号。

但是,接收器和发送器侧都不需要差分终端 — 建议仅在输入端以 100 欧姆进行差分端接。

此外、我对您的上拉和下拉感到有点困惑 (R1925-1926、R1931-1932、R1927-1930 和 R1937-R1940)。 您能解释一下为什么会这样吗? 我相信它们可能会导致不正常和意外的功能。

谢谢、

Michael

非常感谢您的答复。

首先、我来解释一下这些电阻的用途:

R1925–R1926 和 R1931–R1932 :

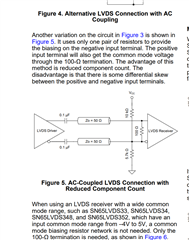

这些电阻器有助于使差分对的直流失调电压更接近。 这种对齐方式可减少迟滞并确保正常运行。 请参阅随附的图像—这基于 LMK00304 主题下同一论坛中的注释:输入 LVDS 交流耦合。

R1927–R1930 和 R1937–R1940:

这些电阻器为接收器提供必要的偏置电压。 由于信号是交流耦合的、因此会阻断直流分量、这些电阻器对于在接收器侧建立适当的共模电压至关重要。

尊敬的 Erdem:

我知道您计划对所有 LVDS 信号进行交流耦合、但这不是我提供偏置电压的方式。 适当的做法是确保在交流耦合后、所有信号都进入共模电压(通常为 VDD /2)。 为此、您可以在每条线路上同时放置上拉和下拉电阻(具有相等值)。 将正极上拉至 VDD、将负极上拉至 GND 是不适当的 — 这将导致接收器只能看到高电平信号并将其拉出。

谢谢、

Michael

我从 如何使用直流和交流耦合端接 LVDS 连接开始 、当然可以很高兴地应用您的 建议

尊敬的 Erdem:

感谢您的关注! 我忽略了该 100 欧姆差分端接的影响(正如我先前所说,最佳做法通常是仅将这种端接放置在接收器侧,如果是这种情况,我的建议将是适当的偏置方法)。

如果您计划在发送器侧保留 100 欧姆端接、则 R1927–R1930 和 R1937–R1940 的偏置配置可以正常工作、但我们建议仅在接收器侧进行端接以减少反射。

谢谢、

Michael