主题中讨论的其他器件:LMX2594、 LMK04832

工具/软件:

我采用了一个 AMD ZCU208 示例设计、该设计将 LMX2594'AS 配置为 400MHz IN、4GHz 输出、并将 LMK04828B 配置为 400MHz out 4MHz sysref。 在 TICS Pro 中、当我加载 LMK04828B_400m_SYSREF_4M.TCS 文件时、会生成以下配置。 有一个指示器表示反馈 PD 频率= 0.5Mhz。 PLL1 锁定为红色文本。 这是否是一个警告、是否应该予以解决? 这个时钟配置确实适用于 ZCU208、并在昨天进行了测试、因此我假设这个示例设计没有问题。

现在、对于我们的实际应用、我们需要使用 LMX2594 生成 1GHz 的频率。 使用 TICS Pro 对它们进行配置似乎效果不错(请参阅随附的 LMX2594_REF-250m-1000m.tcs)。 我还意识到可以选择各种其他输入频率、例如 500MHz、100MHz、50MHz、但我不确定如何评估最佳组合。

e2e.ti.com/.../LMX2594_5F00_REF_2D00_250M_5F00_1000M.tcs

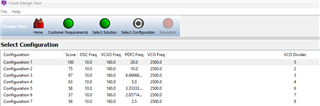

现在、在将 LMK04828B 配置为输出 250MHz 时、我开始手动修改 GUI 中的 400MHz TCS 文件、并且无法像 400MHz 设置一样显示 PLL1 被锁定的组合。 然后、我发现了时钟设计工具、并将其设置为输入 10MHz 和 160MHz、因为这是 CLK104 的设计方式。 生成的配置如下:

我选择了配置 1、因为我认为较高的分数“更好“、只是不确定这是如何量化的。

然后、我将上述设置并将其反向标注到 TICS Pro 中、我保存了该 TCS 文件:

e2e.ti.com/.../LMK04828B_5F00_250M_5F00_SYSREF_5F00_2.5M.tcs

我看到的即时问题是 PLL1 被解锁为红色文本。 我认为我对设置进行了正确的反向注释、并且我尝试了解如何解决 0.15625MHz 的反馈 PD 频率和 PLL1 解锁。

查看我看到的一些多路复用器设置、可以看到增加 PLL1 反馈 PD 的一种方法是不使用 2.5MHz Sysref 作为 PLL1_NCLK_MUX 设置、而是使用 160MHz VCXO(请参阅随附的 LMK04828B_250m_SYSREF_2.5M_PLL1_NCLK_MUX_OSCin.tcs) e2e.ti.com/.../LMK04828B_5F00_250M_5F00_SYSREF_5F00_2.5M_5F00_PLL1_5F00_NCLK_5F00_MUX_5F00_OSCin.tcs

但是、此处不会像之前的设置那样以红色指示 PLL1 锁定状态。 是否真正的验证方法是使用这些 TCS 文件通过 SCUI 或 APU 对 CLK104 进行实际编程、或者是否只能在 TICS Pro 中完成?