工具/软件:

SDIO 在配置之前是否在上电时驱动?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

SDIO 在配置之前是否在上电时驱动?

相关的寄存器字段为 SPI_3WIRE_DIS 和 SDIO_RDBK_TYPE。 POR 默认值指示在启动时启用了 3 线模式、该模式为开漏回读。 因此、如果在启动时或在寄存器复位切换后向 LMK04832-SEP 启动回读事务、SDIO 引脚可以主动驱动逻辑低电平。 直到并且除非发生回读事务、即使使用默认寄存器设置、SDIO 引脚也为 tri 状态(因为它通常必须用作输入)。 当然、当 SPI_3WIRE_DIS=1 时、SDIO 完全用作 tri 状态的输入引脚。

“缓冲输出引脚“是什么意思?

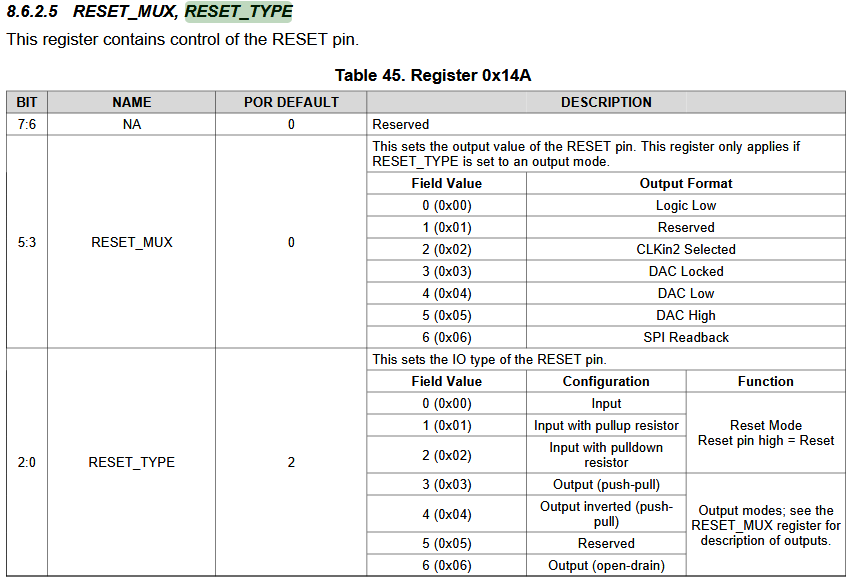

如果您打算在 4 线 SPI 布局中使用其他 GPIO 作为 SDO 引脚、则必须对这些引脚进行编程以多路复用 SPI SDO 信号输出、并且可以根据需要编程为推挽或开漏输出。 多个寄存器字段(从引脚名称开始,到_MUX 或_TYPE 结束)控制引脚的方向和功能。 以下是使用 RESET 引脚的示例:默认值表示 RESET 引脚启动为带有下拉电阻的输入(除非设置为输出模式,否则忽略多路复用器功能)。 要将 RESET 引脚编程为开漏 SPI 输出、RESET_MUX 应设置为 6、RESET_TYPE 应设置为 6(即 0x14A = 0x36)。 可以对任何其他 GPIO (CLKin_SEL0、CLKin_SEL1、STATUS_LD1、STATUS_LD2) 执行相同的过程。

如果您想知道 “缓冲输出引脚“的含义、请告诉我。