Thread 中讨论的其他器件:LMK05318

工具/软件:

有关详细图片、请参阅随附的文件。

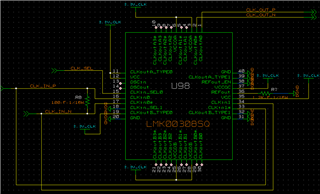

1.我想询问当时钟输入线按如下所示进行配置并进行输入选择时、时钟输出 (CLK_OUT_P、CLK_OUT_N) 会发生什么情况。

1) 向 CLKin0 和 CLKin1*应用相同的时钟输入信号 (CLK_IN_P)

2) 将相同的时钟输入信号 (CLK_IN_N) 应用于 CLKin0*和 CLKin1。

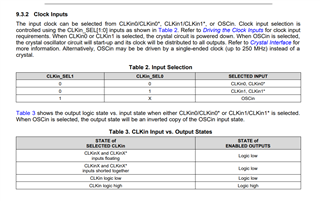

问题 1) 当 CLKin_SEL1=0 且 CLKin_SEL0=0 时、输出信号是什么?

问题 2) 当 CLKin_SEL1=0 且 CLKin_SEL0=1 时、输出信号是什么?

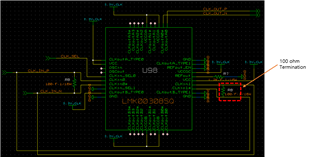

2.在与上一个问题相同的设置条件下、CLKin1 和 CLKin1*之间具有 100 Ω 终端与 CLKin1*之间有什么区别?

e2e.ti.com/.../Question-about-LMK00308.pptx

3. 在与上一个问题相同的设置条件下,您可以在 EVKIT 上测试,并告诉我结果吗?