工具/软件:

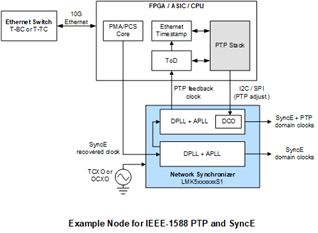

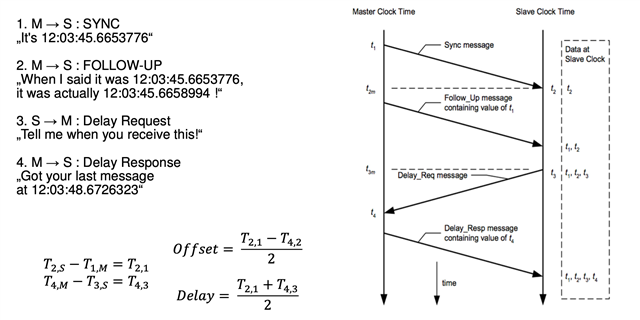

我目前正在尝试使用 Intel i210 同步 Aes67 音频设备的 PTP 时钟输出。 然后由 LMK05318B 对 i210 的基准时钟输出进行滤波/倍频、以便将 I2S 时钟输出到下游器件。

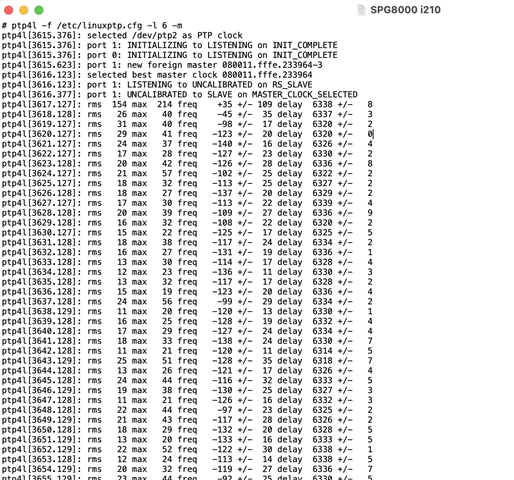

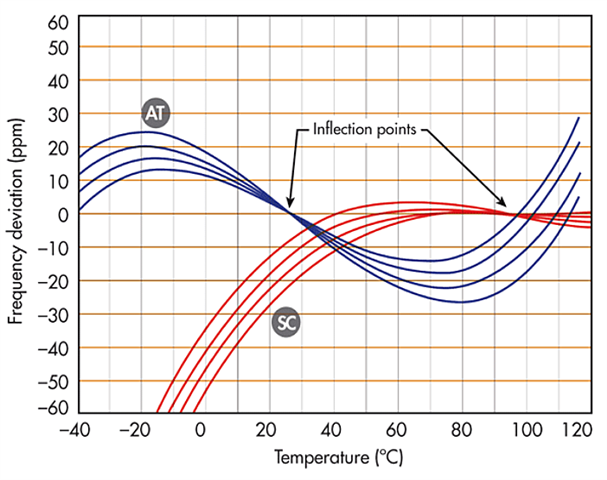

i210 由 x86 Linux PC 控制、并通过 Linux 的 PTP4L 同步外部时钟。 testPTP 程序控制 i210 的 SDP 引脚、以输出 2KHz 方波信号作为 LMK05318B 的基准时钟。 LMK05318B 的 XO 晶体振荡器是 12.288M TCXO

用于测试的 PCB 由我自己绘制、当前用于测试的寄存器配置如下: