请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMX2594工具/软件:

全部、

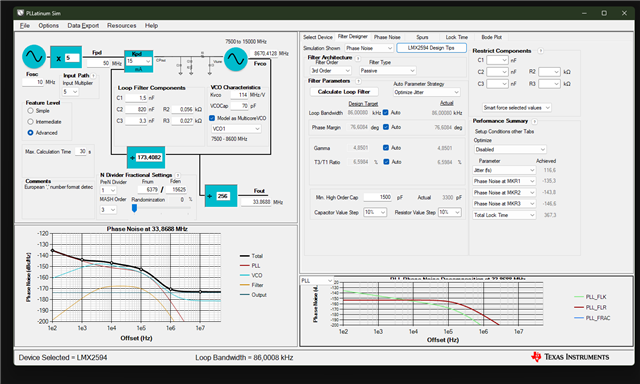

PLLatinum Sim 中的仿真相位噪声 116fs 无法通过测量再现。 您还能否分享您的测试设置以验证相位噪声测量值?

谢谢。此致

Alex

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

全部、

PLLatinum Sim 中的仿真相位噪声 116fs 无法通过测量再现。 您还能否分享您的测试设置以验证相位噪声测量值?

谢谢。此致

Alex

您好 Alex、

需要在仿真中包含基准时钟的相位噪声。

1.创建一个类似如下的文本文件,左侧的偏移频率以 Hz 为单位。

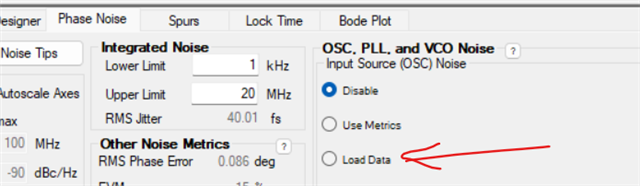

2.将文本文件加载到 PLL SIM 中

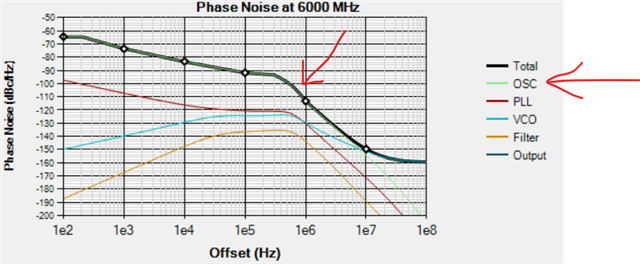

然后可以看到基准时钟的相位噪声贡献、例如、

仿真和实际之间之所以有区别的另一个因素是 10MHz 时钟的压摆率。 PLL Sim 不考虑压摆率造成的影响。 PLL 喜欢高压摆率输入时钟。 PLL 噪声随着压摆率的升高而降低。

如果您必须使用 10MHz 输入时钟、则需要使用方波时钟(如 CMOS 或差分时钟)。

10MHz 正弦波时钟将严重损害 PLL 噪声。