工具/软件:

您好:

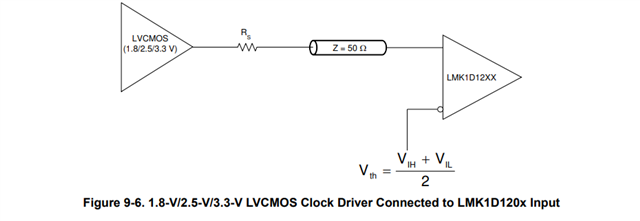

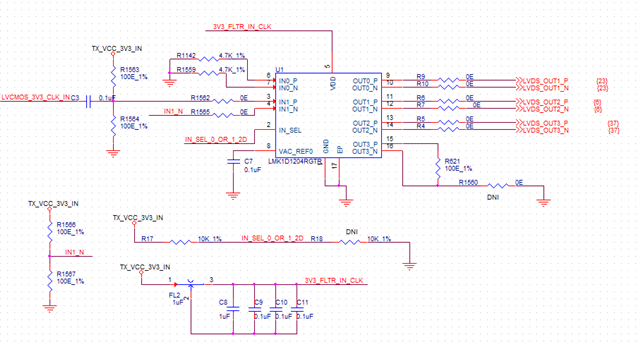

我使用具有 3.3V 振幅的单端 LVCMOS 时钟作为输入。 请查找所附的原理图以供参考。 我有几个关于偏置配置的问题。

当前设置:

-

LVCMOS 时钟信号 (3.3V) 交流耦合至正输入引脚、 IN0_P 。

-

未使用的负输入引脚 IN0_N 将偏置到建议的半电源电压 1.65V。

- 问题:

-

由于正输入 ( IN0_P ) 是交流耦合的、是否还需要为其提供直流偏置? 如果是、电阻器阻值应该是多少?

-

是偏置未使用的输入引脚所需的分压器 IN1_N 在 1.65V 下、或者可以使用另一种方法吗?

-

随附的是上面的原理图。 请查看并告知我此问题是否正确?