Other Parts Discussed in Thread: LMK6H

工具/软件:

高支持

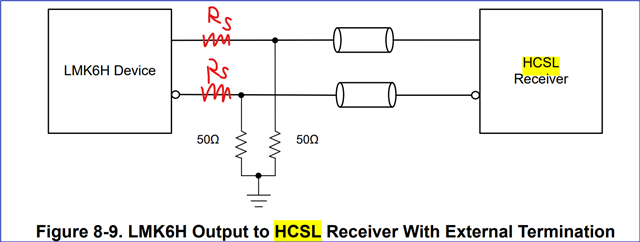

我对 带外部端接的图 8-9 LMK6H 输出到 HCSL 接收器有疑问、最初用于仿真、因此我想进行澄清、因为它看起来与其他供应商的应用手册不同。 我想知道是否应该像我的草图那样存在串联电阻器? 或者 LMK6H 中已经内置了串联电阻?

*我还从其他供应商附加应用程序。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tim:

此处我们提供了 LMK6H 的 PCIe 合规性报告、其中包括频域和时域测量: https://www.ti.com/lit/an/snla445/snla445.pdf

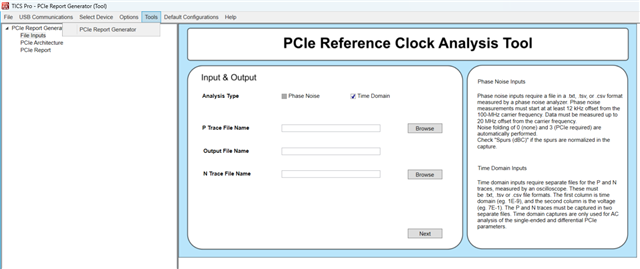

TICS Pro 中还内置了一个工具、可在其中输入相位噪声曲线或从示波器捕获的波形、以检查 是否符合 PCIe REFCLK 规格。 LMK6H 数据表中还包含大多数必要的时域规格((VOH、<xmt-block1>VOL</xmt-block>,交叉点,压摆率等)。VOL。

您可以在以下位置在 TICS Pro 中找到 PCIe 工具:

此致、

Connor