“线程: 测试”中讨论的其它部件

尊敬的技术支持团队:

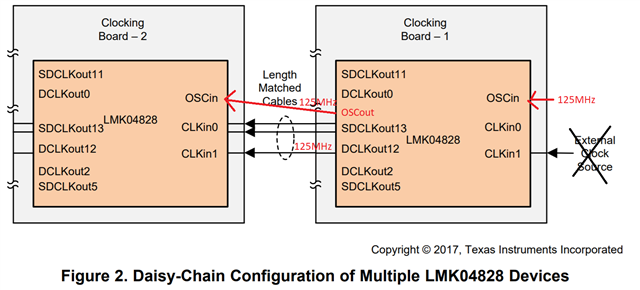

我希望使用两个 LMK04828,并尽可能在输出时钟之间同步。

我的想法是将一个输出(缓冲 LVDS)输入到另一个 clkin0或 clkin1。

由于不使用与 JESD204B 兼容的 ADC 和 DAC,因此将 LMK04828用作时钟发生器,因此不需要同步和 SYSREF。

请参见随附的两个 TSC 文件和时钟树(pdf)。 能否检查 LMK04828的设置?

如果您有在 两个 LMK04828EVM 之间同步的参考设计,您可以共享它吗?

e2e.ti.com/.../LMK04828_5F00_OSCin10MHz_5F00_ADC_5F00_FPGA_5F00_2022.01.07.tcs

e2e.ti.com/.../LMK04828_5F00_OSCin10MHz_5F00_DAC_5F005F00_2022.01.07.tcs

e2e.ti.com/.../0624.LMK04828_5F00_clktree.pdf

此致,

TTD