线程中讨论的其他部件:LMX2820, LMK1D2102, LMK1D1204, CDCLVC1102

你(们)好

我们希望将 PLL LMZ2820用作 sysref 生成器。

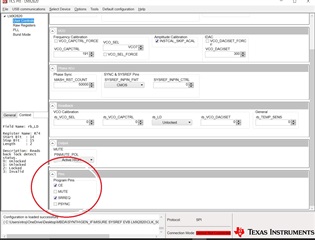

我正在附加 TIC pro 配置文件:sysref 频率约为39 MHz,由内部 VCO 生成。

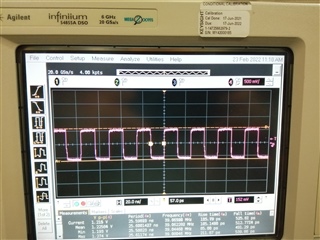

sysref 信号的生成似乎正确(请参阅随附的度量)。

但要生成此信号, SRREQ 引脚需要高电平。 为什么? sysref 来自内部 VCO,而不是 SRREQ 引脚。

这些引脚的含义是什么?

请提前感谢。

此致,

Matteo Ricci

e2e.ti.com/.../CLK_5F00_5G_5F00_FPGA_5F00_312M5_5F00_SYS_5F00_REF_5F00_39M0625.tcs

e2e.ti.com/.../CLK_5F00_5G_5F00_FPGA_5F00_312M5_5F00_SYS_5F00_REF_5F00_39M0625.tcs