请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:CDCLVP1204 “线程”中讨论的其他部件: CDCLVD1204, LMK1D1204

大家好,团队

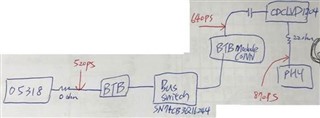

客户希望我们对他们的时钟设计进行双重检查,即05318B (LVDS)-> CDCLVP1204 (LVPECL)-> PHY (LVDS)。 是否可以这样做?

使用 CDCLVP1204而不是 CDCLVD1204的主要原因是 CDCLVP1204的 TF/TR 更快,因此客户在终端接收器 PHY 处有严格的计时要求。

在其原始 PCB 设计中,TR/TF 测试在 PHY 的规格 TF/TR =最大800ps,因此客户希望进行最小变化,看看是否可以解决这个问题,谢谢!

安德鲁