“线程”中讨论的其它部件: CDCE706, CDCE6214

你(们)好

我使用 Vcc=2.5V 的 CDCVF2510来生成 FPGA 的时钟

FPGA 要求此时钟具有高达500ps (10-90%)的趋势

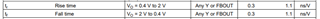

从 CDCVF 数据表看,我发现它的 Vcc=2.5V TR 最小转换率为0.5V/NS。 这将是总和

从0.4 V 上升到1.7 V,几乎达到3 ns!!

有了这种 TR,就无法达到所承诺的170MHz 的 Fmax (5.9nS)

即使我看着最好的转换速率(1.4V/NS),我也面临着大约1ns 的 TR,距离 FPGA 仍然很远,需要500ps。

我的计算是否正确,Vcc=2.5V 的 CDCVF 最佳电流仅为1ns?

如果是,是否有另一个时钟发生器(x5作为最小风扇输出)可以满足 FPGA 要求?

如果有任何关于如何改进我的时间安排的建议,我们将不胜感激

谢谢

阿姆诺