我有一个与上述时钟发生器有关的设计,我们没有差分输出。 我想就这一问题得到一些支持。

设计如下:

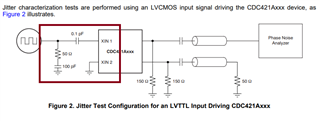

与之相连的内部电路是:

时钟输入基准为31.25MHz,电源和 CE 均为“okey”。

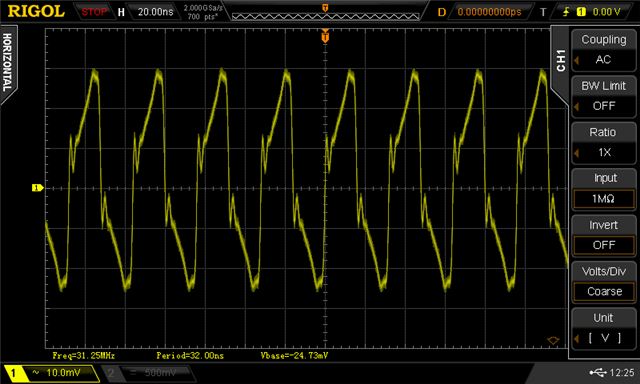

我测量了输入时钟,并检查了3V 偏移。 这可能是问题吗?

提前感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我有一个与上述时钟发生器有关的设计,我们没有差分输出。 我想就这一问题得到一些支持。

设计如下:

与之相连的内部电路是:

时钟输入基准为31.25MHz,电源和 CE 均为“okey”。

我测量了输入时钟,并检查了3V 偏移。 这可能是问题吗?

提前感谢!

您好,

我可能会观察到两个原因:

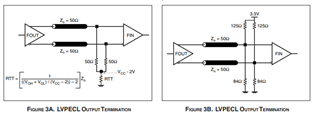

1.对于 LVPECL 输出,接收器端的50欧姆端接应在串联电阻盖后。 在当前配置中,150ohm 和50ohm 并行,这将影响 LVPECL 输出所需的整体端接。

2. X5是 Crystal 还是 LVCMOS 驱动程序? 如果是 Crystal,则按照 Crystal 数据表中的终结选项进行操作。 对于 LVCMOS 输入,请遵循以下电路。

谢谢!

此致,

阿耶特·帕尔

非常感谢 Ajeet Pal 的回答。

1.我无法修改接收器的内部电路,因此系列电阻盖之前的50ohm 端接不能修改。 我可以在这里做些什么? 要在我的外部电路中添加系列电容? 我是指150个终端电阻器和接收器输入之间的电阻。

2.是的,这是一个 LVCMOS 输入,我会尝试重新处理以包括该电路。 串联电容(0.1pF)的值让我认为它只代表线路的电容。 但你是说我应该添加盖子和电阻器,对吗?

3.我需要以下任何外部端接电路吗?

再次提前感谢您。

您好,

[引用 userid="426033" url="~/support/clock-timing-group/clock -an-and -timing/f/clock-timing-forume/1085123/cdc421a156-no-different-output/4018068#4018068]1. 我无法修改接收器的内部电路,因此系列电阻盖之前的50ohm 端接不能修改。 我可以在这里做些什么? 要在我的外部电路中添加系列电容? 我是指150个终端电阻器和接收器输入之间的电阻。 [/引用]是的,您可以在 150个终端电阻器和接收器输入之间放置串联电阻盖。

[引用 userid="426033" url="~/support/clock-timing-group/clock -an-and -timing/f/clock-timing-forume/1085123/cdc421a156-no-different-output/4018068#4018068"]2. 是的,这是一个 LVCMOS 输入,我会尝试重新处理以包括该电路。 串联电容(0.1pF)的值让我认为它只代表线路的电容。 但你的意思是我应该添加盖子和电阻器,对吗?需要使用串联盖来隔离交流耦合模式下输入信号和设备输入针脚之间的共模电平。 分流器50ohm 用于为输入信号提供所需的输入阻抗。

[引用 userid="426033" url="~/support/clock-timing-group/clock -an-and -timing/f/clock-timing-forume/1085123/cdc421a156-no-different-output/4018068#4018068]3. 我是否需要以下任何外部端接电路?对于 LVPECL 输出,已存在150欧姆分流器。 因此,除串联电容器外,无需任何外部电路。

谢谢!

此致,

阿耶特·帕尔

您好,Ajeet Pal,

我会尝试添加该系列 CAP。

我没有输出(只有10mVpp 发出噪音)。

输入时钟参考不是最好的,但我不知道为什么。

我已经检查了耗材和启用情况,一切都很好。 不需要特殊序列,对吗? 我在本论坛的其他一些标签中看到,振荡器的供应在供应时钟发生器之前应该保持稳定,但这与另一个 PN 有关,我使用的设备数据表没有指定任何特定序列。

再次感谢

此致。