主题中讨论的其他部件: CDCE6214

尊敬的技术支持:

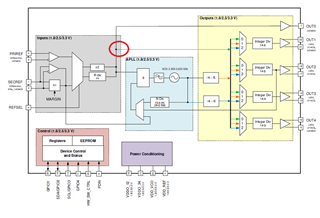

我需要为 英特尔Cyclone 10 GX FPGA提供322.26.5625万 MHz或644.5.3125万 MHz参考时钟,以便与USXGMII接口配合使用。 这是与Marvell的10GBASE-T PHY通信所必需的。

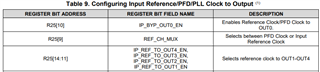

我想使用CDCM6208 V2生成这样的参考时钟,但我找不到任何明确的指示,说明如何在使用输出分整除器时计算抖动/相位噪声。

我发现我无法使用整数除法获得所需的频率。

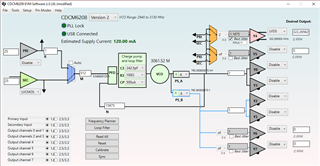

我的想法是 采用以下配置以获得所需的时钟。 我看到EVM软件可以为整数除法器输出绘制相位噪声,但不能为小数除法器输出绘制相位噪声。

我还需要生成其他时钟,例如100MHz,50MHz和其他没有严格抖动 要求的辅助时钟。

您能告诉我如何计算这种情况下的抖动吗?

是否有任何其它TI时钟发生器更适合此应用? 如果可能的话,我更喜欢1.8V的电源。

谢谢你