请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

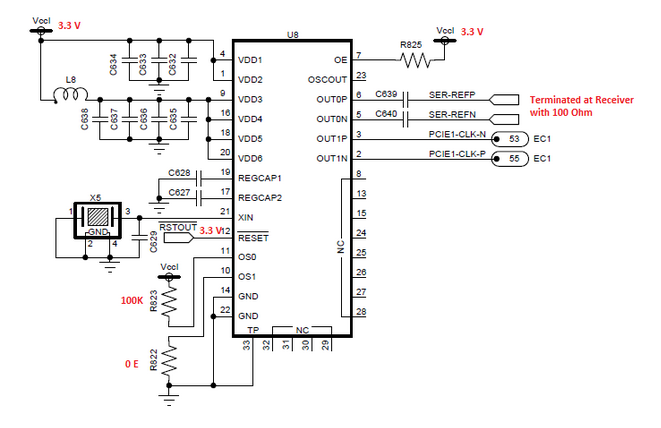

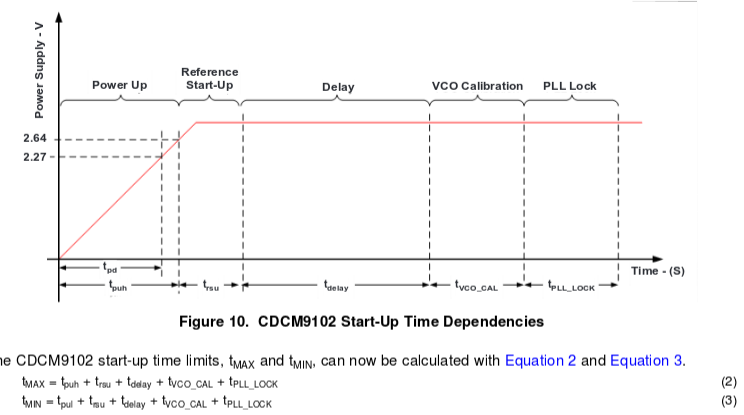

部件号:CDCM9102 我们已针对启动条件进行了测试。 捕获了以下波形。 启动时,在功率上升和RSTOUT断言之间有足够的时间。 请查看波形并提出解决方案。

1.电源Rampup

2.蓝色为电源,黄色为RSTOUT

3.模拟节点(VDD3,VDD4,VD5,VDD6)和IO节点(VDD1,VDD2)。 同时应用所有应用程序。

我们正在满足以下仍不生成差分时钟的要求。

我们在OS0上测试了10K,而不是100k。 我们没有得到差分时钟。 我们在这种特定接口上有着很高的优先级。 请建议我们。

谢谢,此致,

N.V.Subbaiah。