请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMK61E2 在“线程: LMK0.4828万”中讨论的其它部件

您好,

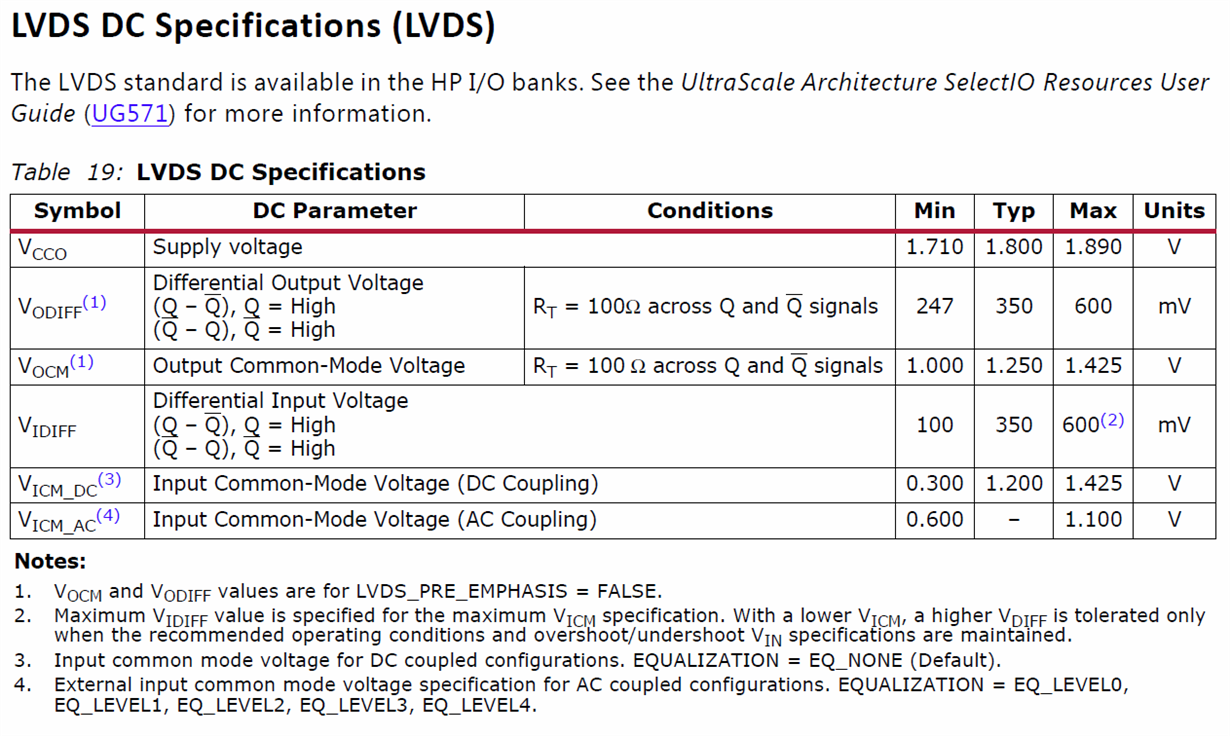

我希望将LMK61E2与Xilinx的Kintex UltraScale FPGA用于原型主板,我对LVDS规范有疑问。 从LMK61E2数据表来看, LMK61E2的LVDS输出特性似乎与FPGA的LVDS规范兼容,但 LMK61E2数据表上有VOUT,差分,PP差分输出峰间摆动规范,使我感到困惑。 VOUT,diff,PP是否指定最大VOH峰间值? 是否有人可以验证LMK61E2是否与下面的FPGA规范兼容?

谢谢!

-Andrew

FPGA规范:

LMK61E2规格: