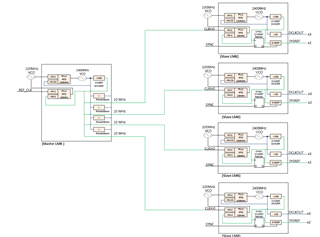

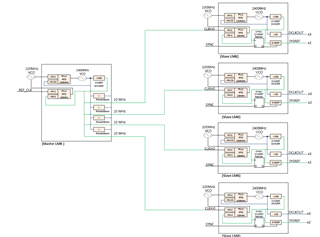

- 一个主 LMK0.4832万驱动上述附加体系结构的4从LMK0.4832万的参考时钟(CLKIN0)。

- 主LMK0.4832万具有到CLKIN0的输入参考时钟和到OSCIN的100 MHz VCXO输入。

- 所有从属LMK将从主LMK输出接收CLKIN0,并将板载100 MHz VCXO输入到OSCIN。

- 所有4个从LMK输出时钟都需要同步和对齐,以便使用零延迟双环模式(ZDM)进行多时钟同步,使用SYSREF_MUX模式进行同步和连续SYSREF。

请验证方案。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请验证方案。

您好,

上述多时钟同步方案看起来很好,其中所有设备都设置为双回路0延迟模式,并将与输入信号同步,并对齐所有从属LMK输出。

有关多时钟同步的应用说明 可能有助于进一步了解0-Delay (0延迟)模式的要求。

只是一个额外的注释,如果系统中没有使用CLKin1,则最好在CLKin1处保留从属LMK输入,而CLKin0可用于同步输入,因为它可以提供非常精确的同步(如果将来需要)。

谢谢!

此致,

Ajeet Pal

您好,

感谢您的意见。

每个从LMK都位于具有FPGA的不同主板上。

您好,

如果0.4832万如果从属405.6366万从属LMKs405.6366万LMKs通过CLKIN0倾斜,则所有从属输出将同步

您是否想在CLKin0上通过参考输入说? 是的,要在双PLL 0延迟模式下使用,所有辅助(从属称为辅助) LMK输出将同步。

如果0.4832万如果每个405.6366万每个从405.6366万从FPGA的T5 LMT5同步输入,即Slave1在T1接收,Slave2[ 在每个T2/t4之间接收同步输出,则Slave2]如果设备配置为0延迟模式,则无需同步输入即可同步。 但对于其他模式,每个次级LMK的同步输入应同时进行,否则每个设备可能会在不同的VCO循环中重置分频器,并且无法同步。

[/quote]Sync_ DISSYSREF0.4832万 DISSYSREF和405.6366万和SYNC_405.6366万SYNC_ DISX是否应该同步设置和CLR? [/引述]SYNC_DISX和SYNC_DISSESREF应是CLR (0),以接收用于重置分禾器的同步输入,并在重置/同步完成后,设置为1以避免任何其他输入。

谢谢!

此致,

Ajeet Pal

您好,Ajeet:

感谢您的澄清。

。在0.4832万在双405.8193万双PLL405.8193万PLL 0-延迟模式下,所有辅助(从属设备称为辅助设备) LMKs输出将同步

如果所有从属LMK都处于双PLL 0延迟模式并 接收到同步参考时钟,则 所有从属输出都将保持同步,而不考虑同步输入。 我的理解是否正确?

在执行“ Multi-LMK0482x/LMK04832 SYNC0.4832万 SYNC ”时,发现以下是建议的Multi LMK同步案例:

其中4a似乎是合适的设计。

如果0.4832万如果设备405.8193万设备配置405.8193万配置为0-延迟模式,则不需要同步输入

如上图所示,同步 也应从主LMK驱动。 如果所有从LMK都接收同步参考时钟,您对此有何看法。

您好,

\n如果0.4832万如果所有408.1893万所有从属408.1893万从属LMK处于双PLL 0-延迟模式并 接收到同步时钟 (无论从属输入是否同步),则同步时钟输出中的所有从属方都将同步。 我的理解是否正确?[/QUOT]正确。 如果设备在嵌套循环双PLL 0延迟模式下运行,则不需要任何同步输入。 它应遵循确定性相位关系的0延迟规则。

[/quote]如0.4832万如上图408.1893万上图所408.1893万所示,同步也应 从Master LMK驱动。 如果所有从LMK都接收同步参考时钟,您对此有何看法。 [/引述]从表中可以看出,Case4a使用单PLL,而上述配置显示双PLL架构。 如果使用单PLL,情况4a应该是好的,并且主LMK的同步输入始终是好的,因此它可以用作嵌套双PLL 0-Delay或情况4a中的情况2b。

对于SYSREF Out本地控制,我建议使用案例2b,它类似于您建议的体系结构。

我认为,对于选项5a,SYNC仅从主LMK驱动用于重新计时的SYSREF。

谢谢!

此致,

Ajeet Pal

您好,

对于0.4832万对于确定408.2494万确定性408.2494万性相位关系,应遵循0-延迟规则。

在我们的情况下,我们将无法遵循0延迟规则,因为从属输出时钟是用户可配置的

即 GCD (CLKIN_FREQ,CLKOUT FREQ)≠ CLKIN_FREQ。

CLKout FREQ是用户可配置的。

因此4a似乎最适合我们,主中继器将采用双PLL架构,从中继器将采用单PLL架构并从主LMK同步输入。

请确认。

您好,

如果辅助LMK在单个PLL中运行,并且没有达到0延迟标准,我的建议将用于4b情况,其中CLKout通道分配器将由重新计时的SYSREF重置。

在单PLL操作中,CLKout相位噪声/抖动性能取决于参考输入频率,应使用更高的输入/相位检测器频率以获得更好的性能。 因此,辅助LMK需要更高的CLKIN_FREQ。

它确保用户配置的CLKout FREQ的选择应考虑到具有选定VCO频率的整数信道分隔器。

谢谢!

此致,

Ajeet Pal