你(们)好

我使用的是 Xilinx ZCU208评估板套件及其包含 LMX2594组件的 CLK104子板。

我尝试使用小数分频器、但由于某种原因、我无法使其工作。

虽然我没有直接测量、因为 CLK104 子板上没有使用合适的连接器、但我正在查看 DAC 的输出采样率泄漏。

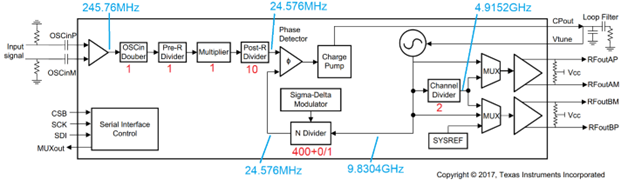

我 使用 Xilinx 提供的预生成寄存器配置、使用以下值生成9.8304GHz 的采样率:

当我更改 N 分频器整数值(例如、从400更改为401)时、我会在 DAC 的输出中看到正确的更新采样率。

但是、当我更改小数部分(寄存器 R38、R39和 R42、R43)时、我看不到任何效果。例如、我使用以下值将小数设置为3/4:

R43:0x2B0003

R42:0x2A0000

R39:0x270004

R38:0x260000

预计为9830.4MHz+0.75*24.576MHz=9.848832MHz、但频率不变。

我缺少什么?