你(们)好。 CLK104板具有 LMK04828B 和板载 TCXO。 我需要将 LMK 与外部10MHz 基准输入配合使用。 尽管我正在禁用 TCXO 并在 TICS PRO 中进行必要的更改、但该器件正在从 TCXO 获取参考。 请帮助我解决此问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好。 CLK104板具有 LMK04828B 和板载 TCXO。 我需要将 LMK 与外部10MHz 基准输入配合使用。 尽管我正在禁用 TCXO 并在 TICS PRO 中进行必要的更改、但该器件正在从 TCXO 获取参考。 请帮助我解决此问题。

HII Ajeet Pal..

我附加了时钟板原理图、使用了 TICS Pro 配置和 CLK104用户指南。

此外、我预计我的 TICS 专业版设置... 请验证。

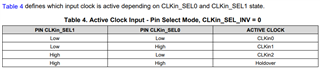

我有几个疑问。 1) 1)是否建议在手动模式下关闭保持、因为我无法确定电路板是否使用外部基准计时? 2) 2)如何设置引脚选择模式、因为我在 TICS pro 中找不到 CLKIN_SEL0_TYPE 的逻辑高电平选项?

所需的 CLK 频率:400MHz,SYSREF:4MHz, 具有10MHz 外部时钟输入,采用嵌套零延迟双环路模式。

谢谢、此致、

信德湖

您好!

您能否通过禁用 TCXO 来确认 PLL1是否锁定? 如何确保 TCXO 在禁用模式下生成输出?

我想、通过禁用 TCXO、您可能会看到 PLL2锁定、但不会看到 PLL1。

但是、在馈送外部单端正弦波输入时、通过在 CLKin0处选择10MHz 外部基准、将 CLKin0_Type 选择为"Bip级"。

关于您的查询:

1.如果要手动选择 CLKinX 输入,可以关闭 Holdover。

2.对于引脚选择模式、请遵循 数据表中的第9.3.5.2节。

谢谢!

此致、

Ajeet Pal

您好 Ajeet Pal、

我通过禁用 Clkin1引脚进行了测试、正如您说的 LED 状态为关闭、因此 PLL1未锁定。

数据转换器逻辑块已准备就绪。 但我需要这些逻辑块在我提供外部10MHz 时钟之前不准备就绪。 因此我禁用了 Holdover 选项。 然后、我希望 PLL2也保持在解锁状态和逻辑块状态-未就绪。 这不是发生的。 我还没有其他东西吗? 我附上了寄存器值供您参考。

最小反馈 PD 频率是多少?

谢谢、此致、

信德湖