Other Parts Discussed in Thread: CDCE6214

主题中讨论的其他器件:CDCE6214

您好!

我需要为 Intel Cyclone 10 GX FPGA 提供322.265625 MHz 参考时钟、以便与 USXGMII 接口配合使用。 从 Marvell 与10GBASE-T PHY 通信需要此功能。

我计划使用 CDCE6214、但我想先获取 EVM 的有效配置。

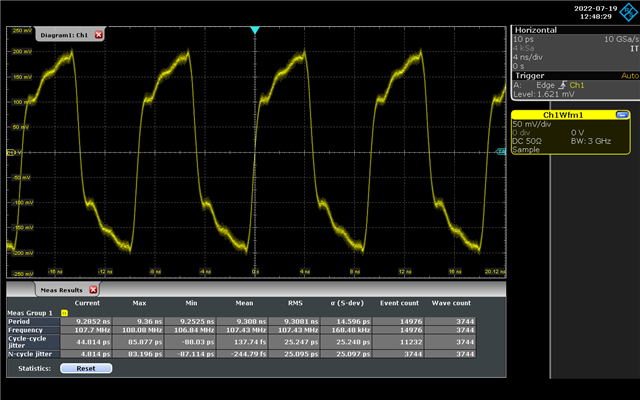

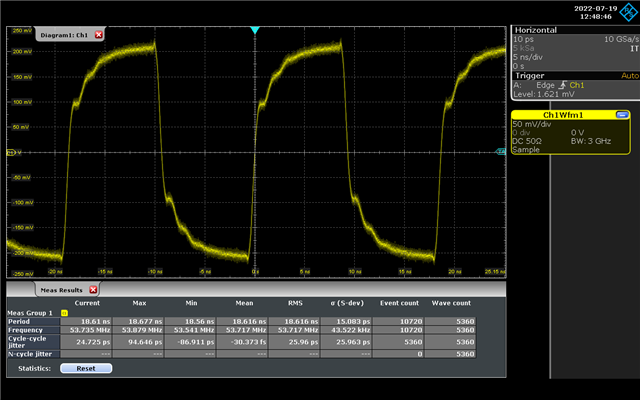

我将使用 Rohde&Shwarz 的 RTO2034测量输出波形、3GHz、10Gsa/s、并使用带宽为3GHz 的有源差分探头进行测量、以实现最大精度。

我将测量配置为 LVDS 1.8V 的 OUT1输出。 我还在电路板上焊接了两个50欧姆端接电阻器(R39和 R43 + 0ohm、R41)、以尽可能获得最佳信号。

CDCE6214配置如下:

-二次参考时为25MHz 晶体

-倍频器/分频器设置为/1 -> PFD 频率= 25MHz

-100uA CP 增益和8.9ns 锁定窗口

小数 PLL 的默认环路滤波器:RP=4.5k、CP=18.72pF、CZ=608.7pF、R3=0、C3=1.2pF

- PLL:整数=103、数字=10000、数字=80000

- VCO 频率= 2578.125MHz

- PSA = PSB = 4

- OUT1:电源= 1.8V、电源= PSA、分频器= 2、驱动器= LVDS 1.8V、输出频率 = 322.265625 MHz

问题是、我测量的输出频率标准偏差约为1.6MHz、这是一个很大的问题!

如果我增大输出分频器(例如、我测试了分频器= 3、4、6 和12)、我会看到输出波形的形状发生了很大变化、频率的标准偏差也会发生很大变化。 分频器= 12时、该频率降至43kHz。

我有什么问题吗? 获得此行为是否正常?

谢谢你

分压器= 2时的输出波形:

分压器= 3时的输出波形:

分压器= 4时的输出波形:

分压器= 6时的输出波形:

分压器= 12时的输出波形:

以下是我当前配置的 TICS Pro 的2个屏幕截图: