Other Parts Discussed in Thread: LMK05318B, LMK5C33216, LMK5B33216, LMK05028, LMK5B12204, LMK04033, LMK04000, LMK04001, LMK04011, LMK04010, LMK04002, LMK04031, LMK04610, CDCE813-Q1

主题中讨论的其他器件: LMK5C33216、 LMK5B33216、 LMK05028、 LMK5B12204、 LMK04033、 LMK04000、 LMK04001、 LMK04011、 LMK04010、 LMK04002、 LMK04031、 LMK04610、 CDCE813-Q1

您好的团队:

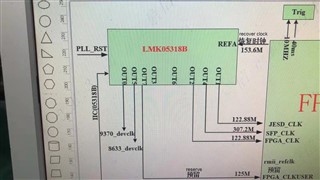

我想确认是否有一个小于1W 的低功耗器件 来替代 LMK05318B。

TKS、供您确认。