您好!

抱歉、如果我在数据表中遗漏了这一点、但我对如何为 LMK04610器件选择 VCXO 以将器件置于抖动清除器模式感到困惑。 我当前的应用有一个时钟输入、该时钟输入可能会因系统的用例而异。 如果我选择 VCXO 进行清理、这是否会限制我可以为系统提供的输入时钟的灵活性?

请告诉我是否需要进一步澄清。

谢谢、

Ryan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Ryan、

考虑到 PLL1_R 和 PLL2_R 分频器、LMK04610支持整数 PLL、这确实需要整数除法输入时钟、即具有集成 VCO 频率的 VCXO。 因此、VCXO 频率应根据所需的 PLL2 VCO 频率和最终所需的输出频率进行选择。 作为抖动清除器、PLL1输入频率可能会有所不同、但它需要更高的分频比、而 PLL1相位检测器频率应变为低电平。

如果您有任何频率计划、可以使用 TICS pro 工具并针对各种输入频率和所需的输出频率对其进行优化。

谢谢!

此致、

Ajeet Pal

您好、Ryan、

PLL2支持5870至6175MHz 的 VCO 频率范围、您的输出频率将是整数除法 VCO 频率。

为了使 LMK04610 (PLL2)具有更好的相位噪声性能、PLL2应具有更高的相位检测器频率(PFD)。 因此、VCXO 频率应尽可能高(IF、任何相位噪声关键要求)、如果可以找到整数除法 VCXO、则可以使用 PLL2_R 分频器并优化 PLL。

例如:fout - 1GHz 要求、您可以选择6GHz 的 VCO 频率并 具有更高的 PLL2相位检测器频率(例如200m)、可以具有100MHz 的 VCXO 频率(使用 PLL2输入倍频器模式)、也可以使用 PLL2输入分频器(PLL2_R)实现其他优化的 VCXO 频率。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

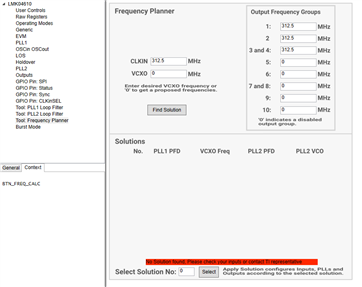

我不得不处理其他几个问题,因此对拖延表示歉意。 我认为您的说法是合理的、但我很难使用 TI 工具(TICS Pro)来帮助您将评论与我们的设计之间的点联系起来。 我正在使用 PLL 的参数、但我仍然迷路了。 此时、我将使用频率规划器、但它并未提及我的输入有任何解决方案。 您是否能够帮助告知我的行为不正确? 我当前的计划是使用两个 LMK04610器件。 一个级联另一个级联。 第一个是我现在尝试设置的内容、它将用作输入频率的缓冲器、并在可能的情况下具有抖动消除功能。 我为 VCXO 频率选择0、以查看它将提供的内容。

再次感谢、

Ryan