各位专家:

你好。 在有关传播延迟的查询中寻求您的帮助:

关于 LM5CN/NOPB 和 LM5CM/NOPB、我想知道从复位下降到开始下降的传播延迟低于1.1V (我可以自己添加15ns 下降时间)。

数据表中未说明我有的 LMC555、数据表版本:SNAS558K–2000年2月–2015年1月修订版。 我在网上或 TI e2e 帖子中未找到任何信息。 [常见问题解答]如何使用 LMC555、TLC555、LM555、NA555、NE555、 SA555或 SE555? 在复位输入对单声道稳定定时器的影响部分中显示了以下内容:"当复位输入变为低电平时、输出将立即变为低电平。"

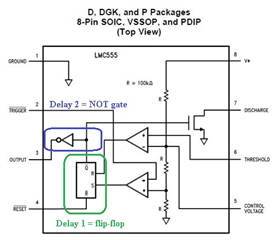

除了作为一个在时序计算中无法使用的无意义的非数值值之外、当我们查看数据表中的简化版原理图时、这显然不是:

我们具有 FF 的传播延迟和非门的传播延迟。 由于该器件必须是 CD4000器件的不同技术、我想(希望)它不是每级250ns 至500ns、更像触发到输出的100ns 传播延迟。

但是、猜测不适合我想要制造的电路(一种沉闷、小、可怜、业余爱好者、家用电容式电表)。 我正在对电路周围的各种"从输入到输出"路径进行各种初步时序计算(基于各类组件使用的数据表规格、如果需要、有时必须根据常见的传感外推进行计算、例如20V 下的 NMOS 数据表规格、~5V 下的750mA、 5mA 电路阻止它驱动...)、但无法计算如果没有任何数字可供使用、复位从低电平拉至输出低电平所需的时间。

我非常感谢此器件的"最低典型值-最高值"测试数据结果、甚至使用相同技术流程从其他器件推断出近似值、我假设 FF 和 NOT GATE 可能是其他 IC 中基于技术/制造流程的标准块、甚至是如此。

我对这个参数的任何数值都很满意、我 可以输入到我需要进行的延迟计算中、这是一个事实准确的数值、也是您自己的明智猜测。

如果需要、该电路将由5V 直流电源供电。

感谢您的支持。

此致、

阿尔基·A.