主题中讨论的其他器件:LMK5B12204

尊敬的专家:

为了针对以下时钟同步情况选择合适的 PLL、我需要帮助:

我在通过10G 以太网连接的远程板之间有以下数据链:

[射频接收器->(jesd204)-> FPGA DSP]->(10G 以太网)->[FPGA DSP ->(jesd204)->射频发射器]

[ 主板 1 ] [ 主板 2]

此外、在菊花链或星型拓扑中、可以插入更多电路板之间、通过10G 以太网传输数据:FPGA -> 10G eth -> FPGA ->……

我想同步所有电路板上运行的时钟、电路板1充当主器件、第二个电路板可能用作回退主器件。

FPGA 是 Zynq UltraScale+ MPSoC XCZU6EG/XCZU4EG

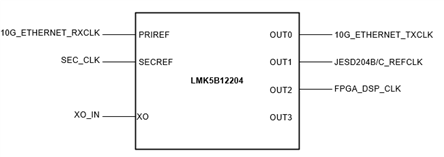

我正在研究 SyncE 或类似的解决方案:10G Rx 时钟恢复、将其馈送到 PLL、从而生成电路板上所需的不同时钟频率。

具体而言:

自由运行时钟生成

输入时钟:

通过10G 以太网从主设备恢复时钟

在第一个主时钟发生故障时切换到第二个主时钟作为回退。

输出时钟:

10G 以太网 TX 的参考时钟

jesd204b/c 的参考时钟

FPGA DSP

此任务的正确 PLL 是什么? 是否有比完全认证的 SyncE PLL 更便宜的解决方案?

最后,在使用 PLL 生成的时钟为 FPGA 计时时,是否存在稳定性问题? 在参考输入时钟开关或失锁的情况下?

非常感谢