主题中讨论的其他器件: LMK5B12204、

大家好、

在我的设计中、我希望使用本地 XO 以及来自 GPSDO 器件的外部10MHz 源(如果存在)生成32MHz 时钟。

在"XO 模式"下、32MHz 精度相对较低、当连接外部源时、32MHz 精度将较高。

外部源可随时连接或断开。

我的问题是-这可以使用 LMK05318B 来完成吗? 如果是、 我不是 PLL 专家-是否有人可以帮助我使用 TICS PRO 向导配置 IC?

非常感谢!

NIR

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

在我的设计中、我希望使用本地 XO 以及来自 GPSDO 器件的外部10MHz 源(如果存在)生成32MHz 时钟。

在"XO 模式"下、32MHz 精度相对较低、当连接外部源时、32MHz 精度将较高。

外部源可随时连接或断开。

我的问题是-这可以使用 LMK05318B 来完成吗? 如果是、 我不是 PLL 专家-是否有人可以帮助我使用 TICS PRO 向导配置 IC?

非常感谢!

NIR

NIR、您好!

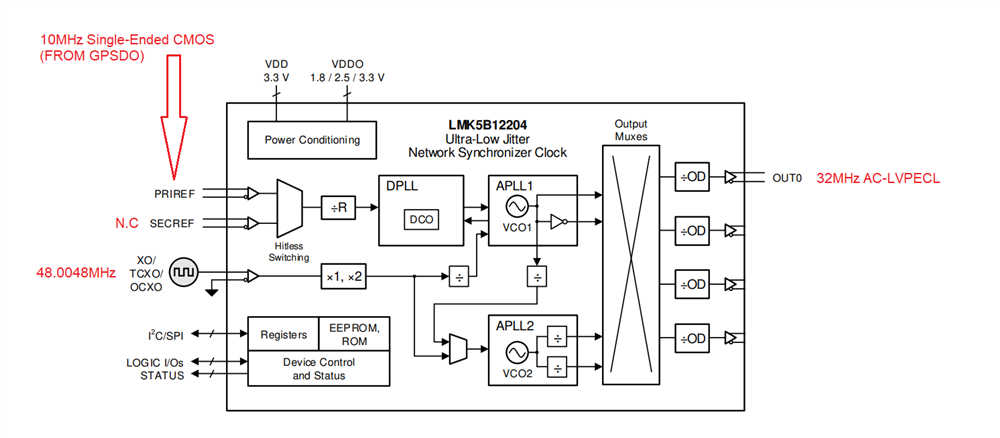

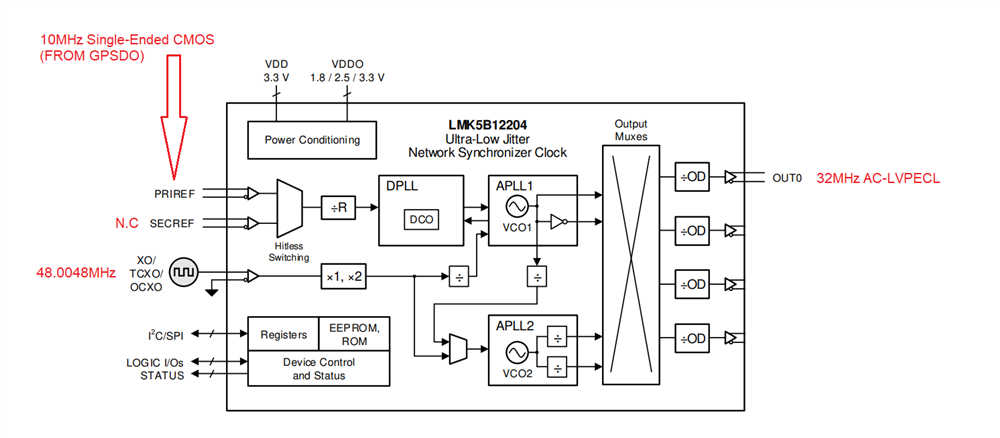

由于您只需要一个输出、因此可以使用 LMK5B12204它是 LMK05318B 的4输出版本。

请查找随附的针对 抖动或功耗性能进行了优化的 LMK5B12204驱动器专业文件。

1) 1)降低功耗

此配置使用 PLL2生成 OUT0=32MHz、并禁用 PLL1以减少功耗。

2)更好的抖动性能

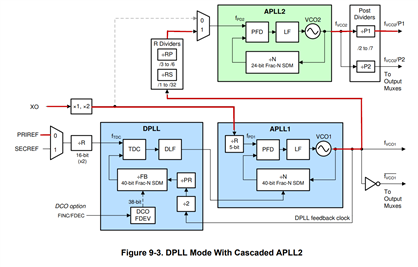

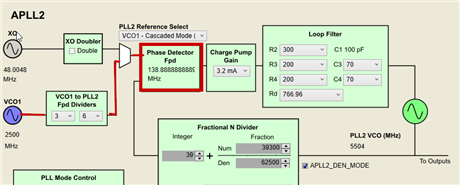

该配置在 OUT0=32MHz 时使用级联 APLL2模式、以利用带 BAW 的 VCO1实现更好的抖动性能。

此致、

Jennifer

NIR、您好!

由于 LMK05318B 版本中有更多的输出、因此将存在一些轻微的系统配置差异。 请改用以下 LMK05318B 配置:

此致、

Jennifer

您好、Jennifer、

嗯、我有 EVM、存在一些问题:

1- LMK05318B_REF = 10MHz_XO = 48.0048MHz_OUT0 = 32MHz_PLL1禁用 、 LMK5B12204_REF= 10MHz_XO = 48.0048MHz_OUT0 = 32MHz_PLL1禁用 似乎不起作用。

我可以看到输出奇怪、但没有32MHz 锁定。

2- LMK5B12204_REF=10MHz_XO=48.0048MHz_OUT0=32MHz_cascadedAPLL2Mode -看起来不错!

3 - LMK05318B_REF = 10MHz_XO = 48.0048MHz_OUT0 = 32MHz_cascadedAPLL2模式 -同样、没有32MHz 锁定、因此我将之前 的 LMK5B12204 脚本与 LMK05318B 进行了比较 、注意到 APLL1和 APLL2上的 XO 倍频器已开启(与 LMK512204 相分离)

我已关闭 XO 倍频器、再次计算频率计划、它解决了问题。

请提出以下几项请求:

您能解释一下这种行为是否正常? 我希望输出恢复到1ppm XO 精度。

此致、

NIR

NIR、您好!

1) 1)我正在研究这个问题。

2) 2) 不知道为什么先前生成的配置启用了倍频器。 不需要倍频 器、因为我们不会将 XO 用于 VCO1级联模式的 PLL2输入。

请尝试新配置。 我已经测试过这个并确认锁定。

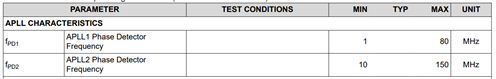

在使用 XO 输入进入 PLL 的情况下、您可以参考以下要求:

3) 3)您是否使用了精度为1ppm 的外部 XO 输入? LMK05318BEVM 中的板载48.0048MHz XO (8W48070002)具有+/-20ppm。 在保持模式下运行时(没有可用的基准输入)、PLL 将锁定到 XO。 输出将根据您观察到的 XO 精度在频率上发生漂移。

您好、Jennifer、

感谢您的支持、

NIR

NIR、您好!

此致、

Jennifer