您好 、Timothy T

我们有一个具有 LMK04828和 RFSoC 的定制板。

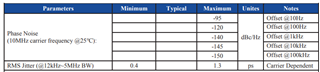

我们观察到、在1K 至100KHz 偏移时、LMK 输出的相位噪声在-95至100dBc/Hz 左右

因此、射频 DAC 输出也具有相同的相位噪声。

下面是所附的 LMK 部分原理图:

我们尝试将 C622的环路滤波器 CP1值更改为680nF、C623更改为100nF、并将 R402更改为39K。 相同的相位噪声结果。

请建议我们如何改善相位噪声。

相位噪声以下供参考。

VCXO 100MHz (Y10)的相位噪声

LMK 输出的相位噪声(DCLKOUT6)- 256MHz

DAC 输出的相位噪声(440MHz)