Other Parts Discussed in Thread: LMK00304

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK00304 您好专家、

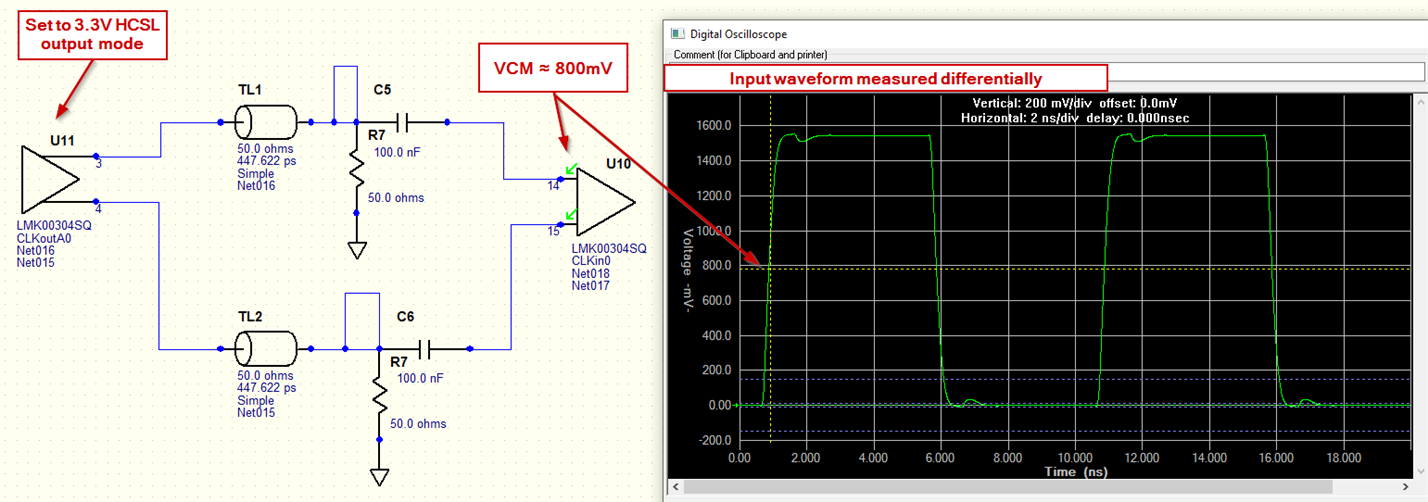

我的 CTM 希望为 LMK00304提供交流耦合输入。 我看到下面的文章说、内部偏置可提供-0.3V 的输入偏移。 我只想确认这个内部偏置为输入提供了共模电压(VCMD>0.25V)、所以不需要外部偏置? LVDS 和 HCSL 信号都能正常工作? 谢谢。