主题中讨论的其他器件: LMK00304、 LMK1D1204、 TIDA-01023

大家好、

我们在项目之一中使用 LMK04828。

Q1:我们有两个从-100MHz 到 CLKIN 的输入时钟 (一个是可选的)、

1、来自外部

板载 VCXO、

我们计划使用开关在两个时钟之间进行选择、作为 LMK 的输入。 您能否向我们推荐可用于在时钟或这些射频开关器件之间进行选择的开关器件、例如 可 使用迷你电路/ Skyworks?

Q2:我们有主从 LMK 配置。

主 LMK 输出时钟将提供给从 LMK 时钟输入。

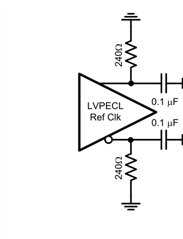

我们将在单端使用受控 LMK 时钟输入、由于我们使用 LMK04828差动输出(LVPECL)、因此我们希望将其转换为单端、以便可以将其提供给受控 LMK。

请建议我们如何将 LMK 的差分输出转换为从器件的单端 CLKIN 信号。

谢谢。