科纳拉德

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Konrad、

在这种情况下、原因并不明显、但 下面是两个实验 、它们可能会引导我们找到根本原因。

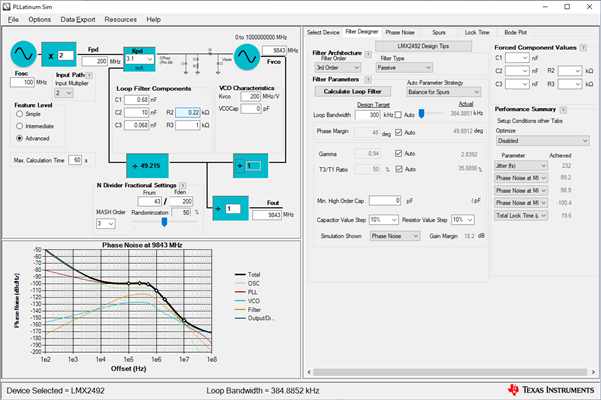

1、理论1: 循环打滑

CSR 不起作用、因此我认为问题不在于周期下滑。 但您可能还需要尝试更改电荷泵电流、以更改环路徽标宽度、而不更改相位检测器频率、而不是 N 分频器或相位检测器频率。 如果您已将其复用、请尝试减小此电流并查看它是否会影响问题。 我希望不是这样,但如果是这样,就重新考虑周期的下滑。

2、理论2: N 分频器

如果存在与 N 分频器相关的问题、 请尝试减小调制器阶数或 PFD_DLY 设置、以查看其是否产生影响。

3、理论3: 误编程

只需确保没有编程问题导致这种情况。

4、理论4: 输入基准

输入倍频器的工作方式是在 OSCIN 的上升沿和下降沿计时。 如果 OSCin 出现问题、例如它没有50%的占空比、则会导致非常高的抖动、可能会导致锁定问题。 要测试此理论、请尝试使用信号发生器进行驱动。

此外、如果问题与 N 分频器或倍频器有关、尝试通过不带倍频器的信号发生器直接传输200MHz 的频率来帮助实现分立。

此致、

Dean