Other Parts Discussed in Thread: LMK00304, LMK00306

主题中讨论的其他器件: LMK00306

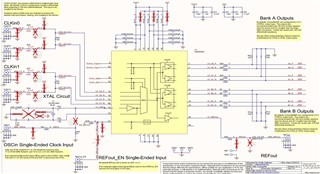

我想使用 LMK00304和 LMK00306缓冲器,但数据表没有具体说明该器件是否具有内部直流偏置。

我希望您能提供有关连接此部件的明确指导。

- 该直流电压是否在内部偏置?

- 如果没有、是否有建议的偏置?

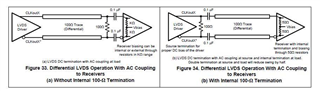

- 如果是交流耦合、则 LVDS 输入:

- 差分网之间是否需要100欧姆电阻?

- 该100欧姆电阻是否应该位于交流耦合器的 IC 输入侧?

此外,数据表中的端接图33和34与我预期的不符。 我下载了该器件的评估板原理图,但它看起来是经过重新设计的,与数据表不匹配… 实际上与我的预期相符。