你(们)好。 借助 Pllaatinum sim 工具、我可以预测相对于环路带宽的输出相位噪声。 但我想知道基准相位噪声对输出射频信号相位噪声的影响。

我想了解基准相位噪声对输出的影响。

根据理论计算、我考虑输出相位噪声=相位噪声(Ref)+ 20log (Fout/Fref)、但我希望通过仿真。 然而、我已经在 llatinum sim 工具中输入了不同偏移处的基准频率相位噪声值、但是输出相位噪声 PLL 没有变化。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好。 借助 Pllaatinum sim 工具、我可以预测相对于环路带宽的输出相位噪声。 但我想知道基准相位噪声对输出射频信号相位噪声的影响。

我想了解基准相位噪声对输出的影响。

根据理论计算、我考虑输出相位噪声=相位噪声(Ref)+ 20log (Fout/Fref)、但我希望通过仿真。 然而、我已经在 llatinum sim 工具中输入了不同偏移处的基准频率相位噪声值、但是输出相位噪声 PLL 没有变化。

您好、Singam、

您可以尝试更改所有字段、也可以在参考输入信号的多个点使用 PN 加载数据。

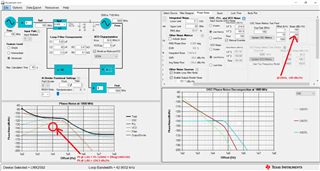

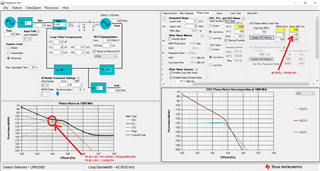

在这里、我要附上 Pllaatinum sim 文件 FYR 示例、您可以在其中尝试更改 REF @10kHz 的 PN、并查看响应。

e2e.ti.com/.../LMX2592_5F00_sim.sim

以下是偏移为10kHz 时 REF 的2个 PN 点的波形图、并查看变化。

希望能澄清您的疑问。

谢谢!

此致、

Ajeet Pal