尊敬的专家

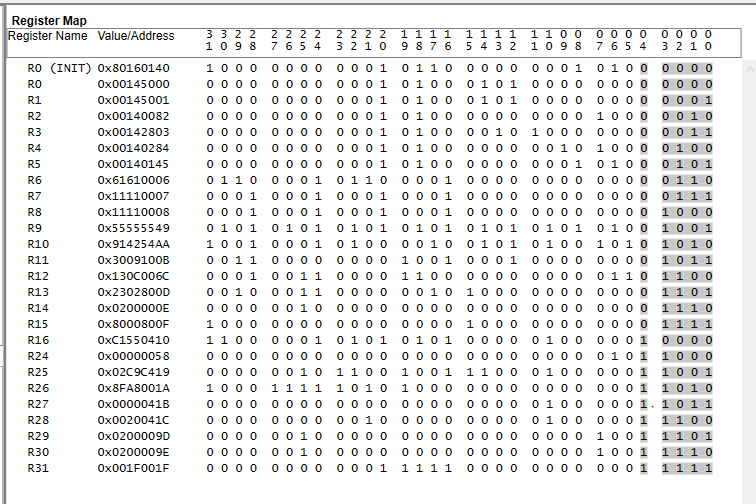

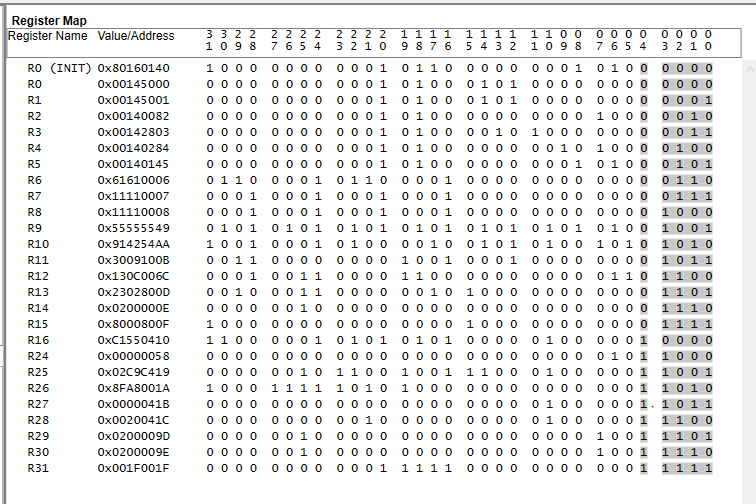

对寄存器 R0的读取和写入不一致(写入0x00145000、回读0x80000320)、其他寄存器的读取和写入也一致。根据下表、写入寄存器的顺序从上到下。CLKoutX_Y_DIV 和 CLKoutX_Y_DDLY 无法写入 R0寄存器。

PLL 在0延迟模式下通常会失去锁定。但是、在正常模式下、PLL 尚未失去锁定。这两者之间没有区别、除了寄存器配置。原因是什么?制造商能否给出一组 C1、C2、R1的建议值(PDF=80MHz)?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的专家

对寄存器 R0的读取和写入不一致(写入0x00145000、回读0x80000320)、其他寄存器的读取和写入也一致。根据下表、写入寄存器的顺序从上到下。CLKoutX_Y_DIV 和 CLKoutX_Y_DDLY 无法写入 R0寄存器。

PLL 在0延迟模式下通常会失去锁定。但是、在正常模式下、PLL 尚未失去锁定。这两者之间没有区别、除了寄存器配置。原因是什么?制造商能否给出一组 C1、C2、R1的建议值(PDF=80MHz)?

您好 Gabriel、

[引用 userid="470630" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1050180/lmk04806-problems-encountered-in-lmk04806-debugging ]1. 寄存器 R0的读取和写入不一致(写入0x00145000、回读0x80000320)、其他寄存器的读取和写入也一致。根据下表、写入寄存器的顺序从上到下。CLKoutX_Y_DIV 和 CLKoutX_Y_DDLY 无法写入 R0寄存器。[/引用]请注意、在 TICS Pro 中、R0 (INIT)寄存器的用途是对所有寄存器进行编程时、它还会通过设置 R0的位17来导致器件复位。 然后、R0寄存器将在下一行写入预期值。 因此、当更改 CLKout_0_1_DIV 和 CLKout0_1_DDLY 时、您应该会在 R0寄存器上看到更改。 我是否了解在输出页面上更改这些字段、是否不更新 R0? 请注意、其他 CLKout_X_Y DIV 和 DDLY 将影响其他 Rx 寄存器。 将鼠标悬停在控件上时、在左下角、您将看到一个上下文帮助、该帮助显示将被更新的寄存器和位置。

您能告诉我有关您如何执行回读的更多信息吗? 我注意到、在图片中、R11/R12/R13的设置不包括任何输出引脚作为 UWire 回读。 您是否有任何示波器屏幕截图显示回读时间? 当然、所有其他寄存器都可以回读是可疑的。 如果反复读取 R0、是否仍然得到错误的值?

您能否详细说明失去锁时会发生什么? 您是否看到 PLL2_LD 信号变为低电平? 您是否测量了时钟频率误差? CPout 引脚电压是否显著变化(电源轨为高电平或低电平?)。

[引用 userid="470630" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1050180/lmk04806-problems-encountered-in-lmk04806-debugging ]2. PLL 在0延时模式下通常会失去锁定、但在正常模式下、PLL 尚未失去锁定、二者之间没有区别、寄存器配置除外、原因是什么?[/QUERP]这是否间歇性地持续几秒钟、它会再次锁定?

[引用 userid="470630" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1050180/lmk04806-problems-encountered-in-lmk04806-debugging "]制造商是否可以为 C1、C2、R1提供一组建议值(PDF=80MHz)?但是、您是否可以试用 PLLATINUMSIM-SW 进行环路滤波器设计?

73、

Timothy

尊敬的 Timothy

感谢您的回复!

1.R0写入错误已被解决、这是由错误的写入时序引起的

在0延迟模式下、PLL 通常会按如下方式丢失

(1)寄存器配置完成后、PLL2_DLD 的指示灯将闪烁

(2)在 PLL 锁定的情况下、输出频率将会偏移、例如、如果设置为1MHz、输出可能为1.03MHz

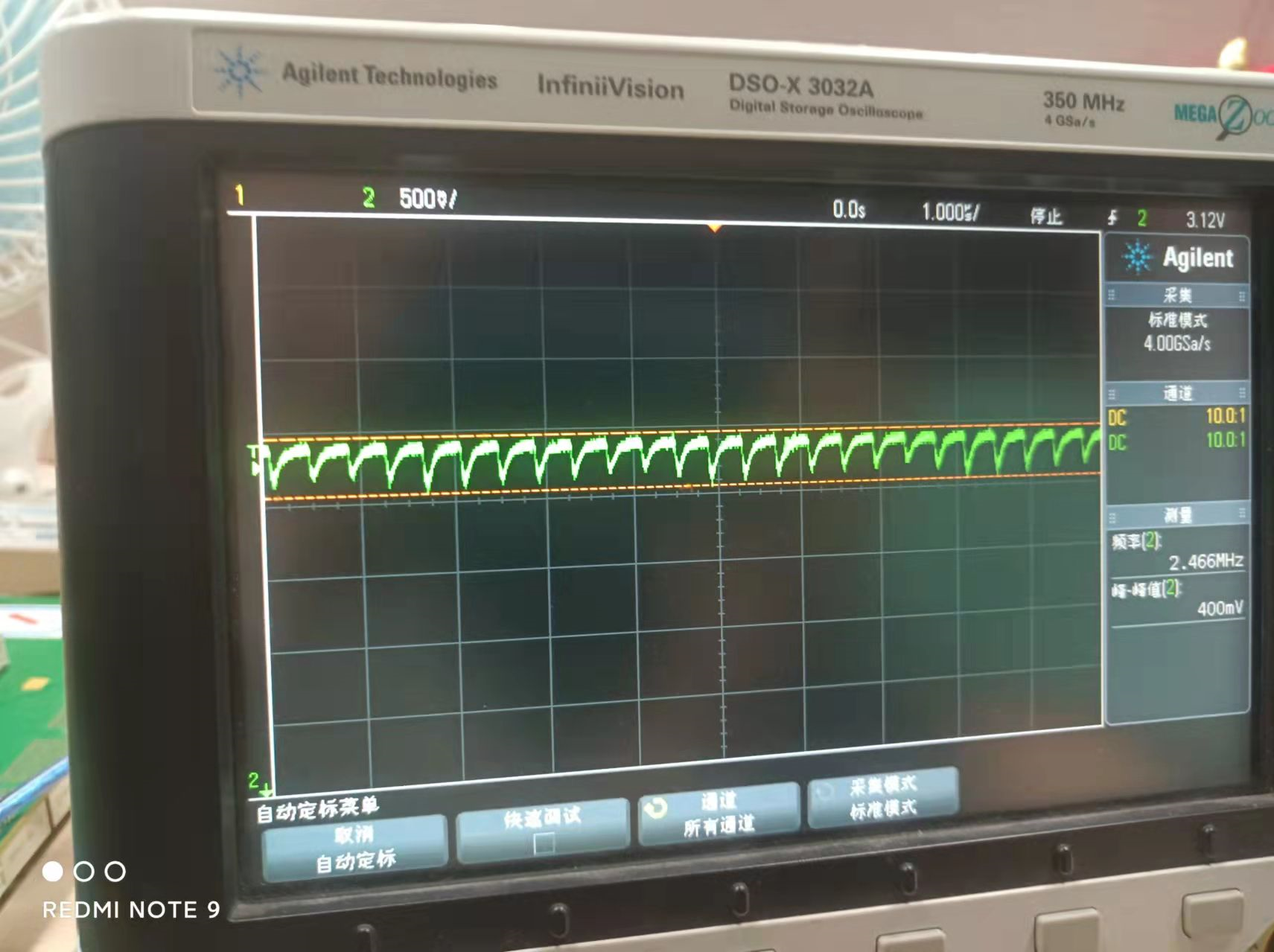

(3)当 PLL 失锁时、环路滤波器的输出通常包含交流分量。如下图所示

(4)外部环路滤波器的 R1、C1和 C2值对 PLL 锁定影响很小

尊敬的 Julian

供参考。