你(们)好

我有一个3.3V OSC、我想从这个 OSC (在其"CLK"引脚上)馈送 CDCVF2310PW。

但是、需要时钟的目标 FPGA 在2.5V 电压下工作、因此我想从 Vdd=2.5V 为 CDCVF2310PW 驱动器馈电。

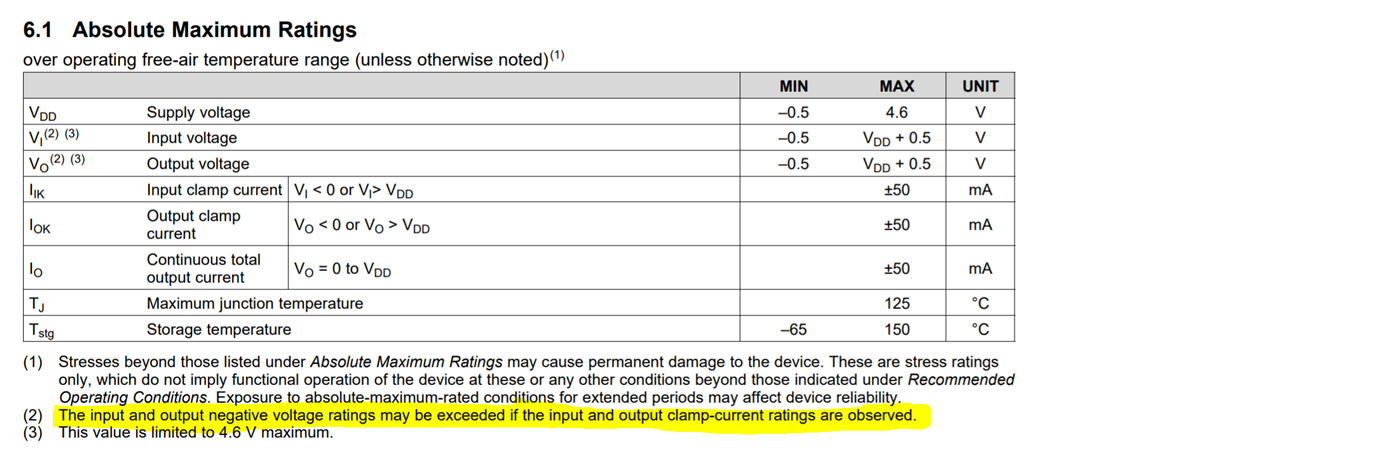

我的问题是 CDCVF"CLK"引脚上允许的最大电压电平是多少?

我在数据表中看到 VIH_MIN 为1.7V,没有 MAX,但 VI (输入电压)受 Vdd (2.5V)的限制,因此将3.3V 时钟馈入2.5V CDCVF 似乎不是正确的设计,对吧?

是否有建议在不更改组件的情况下绕过此问题(OSC Vdd 需要3.3V 电压、FPGA 需要2.5V 输入时钟)?

谢谢

Amnon