大家好、

我对 LMK04828中的 CLKin0/0*输入有疑问:

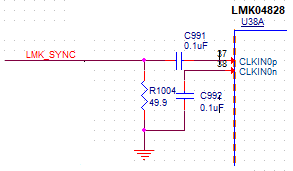

我们通过交流耦合并在其 MOS 模式下(CLKinx_type=1)驱动它。

CLKin0*通过一个电容器连接到 GND。

我们希望对其进行正确偏置、因此当 CLKin0/0*上没有活动(交流耦合电容器处于切断状态)时、不会发生误触发(噪声等)。

我认为不允许分别在 CLKin0和 CLKin0*上连接 PU 和 PD、因为|VCLKinX-OFFSET|在这些引脚之间的典型值为55mV。

我们应该如何处理这种针对无活动情况正确偏置输入的情况?

谢谢!

吉尔