主题中讨论的其他器件: ADS42JB46EVM、 LMK04832、 CDCLVP111-SP、 LMK03328、 ADS42JB46

大家好、

1) 1)我不知道 LMK04828 (在 ADS42JB46EVM 中)的设计原理图中为什么有3种"阻抗匹配"、因为我认为时钟输出引脚是相同的。

2) 2)我应该如何为阻抗匹配选择电阻大小、因为我不知道传输线路的特性阻抗。

感谢所有回复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

1) 1)我不知道 LMK04828 (在 ADS42JB46EVM 中)的设计原理图中为什么有3种"阻抗匹配"、因为我认为时钟输出引脚是相同的。

2) 2)我应该如何为阻抗匹配选择电阻大小、因为我不知道传输线路的特性阻抗。

感谢所有回复。

Nan、您好!

此致、

Derek Payne

尊敬的 Derek:

我还有其他一些 我不知道的问题、

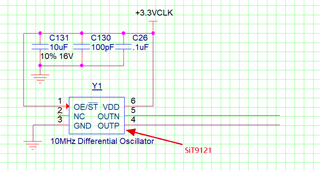

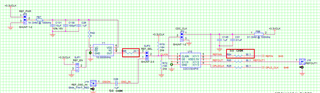

1) 1) 现在我想使用10MHz 振荡器(图1中的 SPT9121)作为 LMK04828的输入时钟、 我是否可以将此振荡器的输出配置为 图2中所示的 ADS42JB46EVM? 这也是 关于"阻抗匹配"的东西? 我是一个新生,不是很了解。

2) 2)我发现100MHz VCXO 会产生一对差分时钟信号、但仅使用其中一个信号作为 LMK04828 (OSCIN)的输入、所以为什么、、差分信号输入有什么问题?

Nan、您好!

此致、

Derek Payne

尊敬的 Derek:

非常感谢、

关于问题1、我可能需要其他时间来理解、但我已经得到了我想要的。 那么、您的意思是、我可能不需要使用~10pF 的负载电容、因为 SiT9121是差分 LVPECL/LVDS、而不是 LVCMOS?

关于问题2、您的意思是 ADS42JB46EVM 上的 VCXO、它有4个引脚、但占用空间 有6个引脚、因此如果我选择6个引脚的 VCXO (具有差动输出)来替代4个引脚部件、它也可以工作、对吧?

再次感谢、

非

NaN、

对于问题1、负载电容通常是 接收信号的任何器件的引脚电容、无论是 LVCMOS、LVPECL 还是 LVDS。 通常 、 无需或没有理由在预先存在的引脚电容之外向接收器添加额外的负载电容、因为通过添加串联电阻器可以实现相同的效果、 加上放置在负载附近的串联电阻器有助于降低反射的影响这一额外优势。 向 LVCMOS 添加串联电阻确实是有意义的。 LVDS 由电流控制、可在100Ω Ω 端接时在接收器产生特定电平。 LVPECL 输出结构设计为在宽传输线长度范围内、差分对每个桥臂(或100Ω Ω 差分、如上所述、通过一些发射器电阻器调整)上的50Ω Ω 单端终端内清晰运行。

关键点:大多数 LVCMOS 驱动器不适用于50Ω Ω 阻抗负载。 当输出级是一个将 FET 连接到 VCC/GND 的推挽结构时、很难将两个 FET 的阻抗始终控制为50Ω Ω 源极和接收极、因为 FET 的阻抗将随其上的电压而变化。 因此、LVCMOS 实际上仅用于低频时钟或较高频时钟的短运行、 以及串联电阻等技术以减少振铃、因为它不能在较高频率下工作、而不会显著降低信号质量、增加反射以及在较高频率下丢失谐波。

因此、 您不需要任何额外的负载电容、接收器的引脚电容将已经加载驱动器的输出。 用于 LVCMOS 的串联电阻器只是为了帮助输出级上的反射、而输出级根本不能具有良好控制的输出阻抗。 LVPECL 和 LVDS 在整个频率范围内对输出阻抗具有良好的控制、因此它们通常在端接之前不需要或不需要在信号路径中使用串联电阻器。

问题2。 您对我的理解正确。 Crystek CVHD-950等4引脚器件或 Crystek CVPD-922等6引脚器件都可以很好地与6引脚封装配合使用;您只需在6引脚器件到 OSCIN_P 的路径中填充其他组件即可。

此致、

Derek Payne

NaN、

为了缩短讲述时间、120Ω 在交流耦合 LVPECL 输出中实现了最接近数据表的摆幅值、但240Ω 交流耦合通常足以满足要求并显著降低电流消耗。 请参阅 https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/759686/lmk04828-proper-emitter-resistor-for-lvpecl-output

与240Ω Ω 发射极偏置电阻器耦合的直流耦合通常也最适合实现与数据表相同的摆幅和 VOH/VOL。 如果您进行数学计算、您将发现此配置实际上具有输出引脚灌电流; 实际上、输出驱动器级内的实际电路设计通常不仅仅是晶体管发射极、因为多模式输出驱动器必须支持 LVDS 或 HSDS 等其他推挽式架构、因此输出电平设置为 LVPECL 时的灌电流仍然是可能的。

此致、

Derek Payne

NaN、

具体取决于使用的器件和输出驱动器规格。 不同的制造商、甚至同一制造商内的不同团队都可以生产不同的 LVPECL 实现。 还有针对2.5V LVPECL 输出的 I/O 标准、对于这些标准、VCC - 1.3V 大约以输出共模为中心。 对于120Ω 所有的 TI 时钟器件、包括 LMK04828和 LMK04832、具有240Ω Ω 发射器电阻器至 GND 的 LVPECL 为3.3V LVPECL 提供适当的交流耦合摆幅、而 Ω 至 GND 为直流耦合3.3V LVPECL 提供适当的共模和摆幅。 LMK03328或 CDCLVP111-SP 等一些器件由于不同的 I/O 电平或替代(也很旧)电源偏置方案而具有不同的行为。 当然、其他制造商的 LVPECL 实施可能会有所不同。

此致、

Derek Payne

NaN、

如果 PECL 接收器不是自偏置、R2/R3很重要。 为了方便起见、许多现代接收器在 IC 的输入级内实现 R2/R3组合、或者实现某种"通用"输入接收器、该接收器可接受多种不同的输入格式。 您通常需要检查接收器数据表中给出的输入信号要求。

在交流耦合 LVPECL 输出中、选择 R1发射器电阻器接地完全可以提供适当的信号摆幅、因为驱动器和接收器之间的电容器可以阻止任何共模差异。 由于2.5V LVPECL 和3.3V LVPECL 标准都实现了~800mV VOD、因此 TI LVPECL 输出级的120Ω Ω 发射极电阻器仍然有效。

在直流耦合 LVPECL 输出中、尤其是从3.3V 转换为2.5V I/O 标准或将 LVPECL 连接到直流耦合 LVDS 时、可以使用一些电平转换技巧、这些技巧将影响发射器电阻器偏置选择。 在这些情况下、实现正确的共模通常比 LVPECL 的完整振幅更为关键。 这些直流耦合电平转换的压摆率有时会由于幅度减小而降低、这会增加相位噪声。 大多数时候、将 LVPECL 与接收器进行交流耦合以接受 LVPECL 振幅更有意义、并在 LVDS 等信号摆幅受到限制时使用不同的 I/O 标准。

此致、

Derek Payne

NaN、

您需要询问数据转换器团队为何在 EVM 上选择150Ω Ω。 大多数情况下、数据转换器团队不太关心具体匹配规格、更关心的是获得足够高的压摆率和信号摆幅以满足其数据转换器时钟要求。 这些参数在很大程度上依赖于过程、我们的数据转换器使用多种不同的过程、这些过程可能具有非常不同的信号摆幅和振幅要求

换言之、不要为了获得理想的发射极电阻值而被带走。 我已经看到120Ω、150Ω、180Ω 和240Ω 全部在 TI EVM 上使用、无论是否符合标准、都不会对相位噪声性能产生太大影响、因为大多数数据转换器的输入级很少需要完全符合标准的 LVPECL。

此致、

Derek Payne