主题中讨论的其他器件:LMK04803、

你好

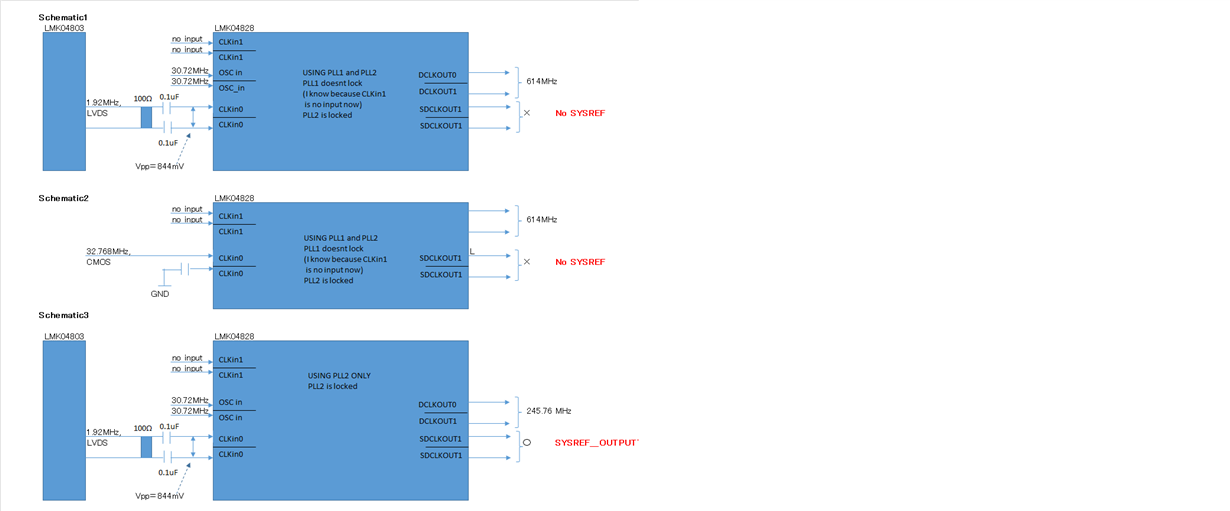

现在我尝试"直接 sysref 模式"、但它不起作用(无输出、信号固定为低电平。 输入同步信号为高电平。)

我的配置如下所示。 (SYSREF 信号连接 到 Clkin0)

0x143 0x10 SYNC_MODE

0x139 0x04 SYSREF_MUX、SYSREF CLKin0_MUX

0x147 0x18 CLKin0_OUT_MUX

0x104 0x20 SDCLKoutY_DDLY

0x140 0x07 SYSREF_DDLY_PD、PLSR、PD

0x106 0x30 SDCLKoutY_PD

0x107 0x55 SDCLKoutY_FMT

请告诉我错误的地方吗?

武城