大家好、

我目前正在使用 LMX2491 PLL。 最近出现了一些问题、我想知道它是否与该组件的启动过程有关、但遗憾的是、数据表中没有给出有关启动和/或启用时间的信息。

更多详细信息:

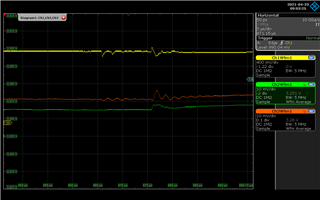

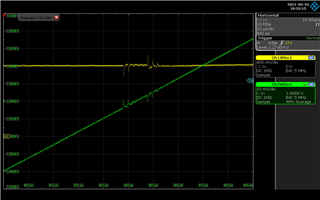

我们将 LMX2491用于 FMCW 雷达应用 、但会看到 IF 信号受到一些干扰。 进一步的研究表明、在 CPout 引脚上测量的 VCO 调谐电压也可以看到这些电压、如下面的示波器屏幕截图中所示(绿色曲线=调谐电压、黄色曲线= IF 信号)。

µs µs 干扰始终同时出现(在 PLL 打开后、介于800 μ s 和900 μ s 之间、在不同示例之间有所不同、但针对特定情况进行了固定)。 此时电源电压干净。

为了更好地理解:我们仅在短时间内为 PLL (或整个射频电路)供电。 加电后、系统等待 PLL 锁定信号并启动斜坡。 发送一个斜坡后、系统断电(Vcc 关闭)。

如果 PLL 连续通电、则干扰仅在稳压器加电后发生一次。

这些结果使我们得出结论、PLL 本身内部会发生一些事情。 有没有人会对这种情况有所直觉? 是否仍有一些启动过程正在进行? 或者是否有关于器件启动时间的信息?

谢谢、致以最诚挚的问候

Chris