主题中讨论的其他器件: LMX2430

大家好、

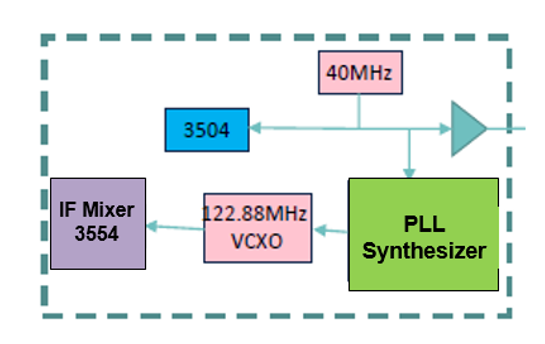

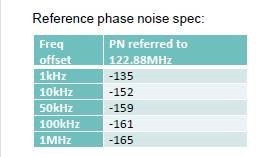

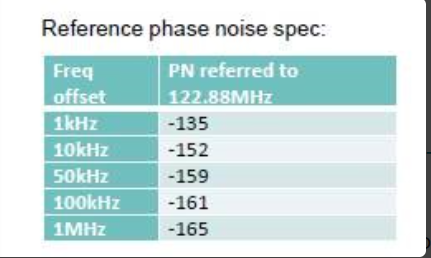

我的客户正在寻找 PLL 合成器。 相位噪声规格和方框图如下图所示。

最初、他们将 ADF4002和 ADF4150用于旧设计。 但是、它看起来总相位噪声将被限制在

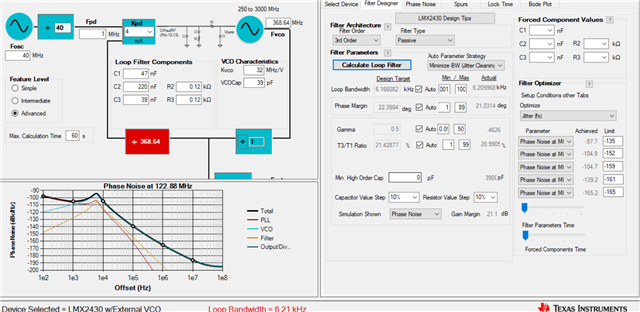

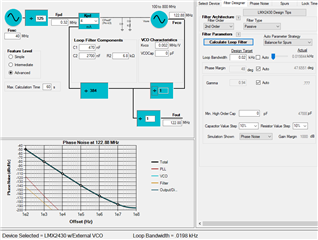

ADF4002的 PN 性能。 ADF42.4的芯片 PN 在122.88MHz 时优于 ADF4002。 VCO RFin 应根据可编程除法设计设置为983.04Mhz、输出为1/2/4/8/16。 根据仿真结果,总相位噪声将被限制为 VCXO PN 性能,如表所示相位噪声和抖动数据。 我搜索了我们的解决方案并提出了我们的 LMX2571。 从规格和成本角度来看、我们是否有更适合其设计的解决方案? 谢谢。