您好!

我尝试在单环路模式下使用 LMK04828、以便从100MHz OCXO 生成1GHz 系统时钟。 OSCin 的输入为100MHz 正弦、1.5Vpp。 PLL2的配置为 R=1和 N=30 (预分频器中为/2、主分频器中为-15)。 我选择了 VCO1、它应锁定在3GHz、然后将其分频至1GHz、并在输出分频器中使用其他一些频率。 我具有如下环路滤波器

- R2 = 560R 外部

- 内部 R3 = R4 = 200R

- C1 = 68pF 外部电容

- C2 = 4.7nF 外部

- C3 = C4 = 10pF 内部

时钟设计工具告诉我、这应该提供191kHz 的环路带宽和68.7度的相位裕度。 我自己在 SPICE 中对方框图进行的仿真得出的数字几乎完全相同。

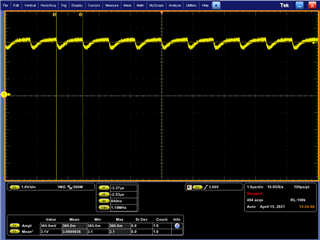

问题是 PLL 拒绝锁定。 DLD 输出保持低电平、并且 CP2OUT 上的电压为~0.36V 斜坡波形、频率为1.2MHz、位于3.3V 电源轨正下方。

我尝试在 Status_LD1引脚上放置 PLL2_R 和 PLL2_N 信号。 PLL2_R 是一个干净的100MHz 方形。 PLL2_N 为101.2MHz、给出了/30的比率会将 VCO1置于3036MHz。 使用 FFT、您可以清楚地看到1.2MHz 调制的边带。 这在 PLL2_R 上不存在、这是死区清理。

这看起来像是环路不稳定、但我不明白为什么 CDT 显示我有足够的相位裕度。 我已经检查了 PLL2是否设置为负斜率(PLL2_CP_POL=0)、OSCin_FREQ=1是否设置为100MHz 输入。

我还注意到、即使应该启用 DCLKx 和 SDCLKx 输出、我也不会获得任何结果。 在 PLL 锁定之前、我在数据表中看不到任何表明这些被禁用的内容。 这是正常的、还是可以指出一些更大的问题?

谢谢、

Tom