请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2820 主题中讨论的其他器件: LMX2594

您好!

我在 LMX2820寄存器映射中找到了"PSYNC_INP_FMT"字段 R68寄存器的说明:

"设置 PSYNC 引脚输入格式。 0x0 = CMOS 输入、1.8V 至3.3V 逻辑;0x1 =交流耦合差分 LVDS 输入、需要外部100 Ω 差分终端"

我的同步源是 LVDS、我不希望使用额外的电平转换器。

您能否提供从差分 LVDS 源驱动单端 PSYNC 引脚的原理图示例?

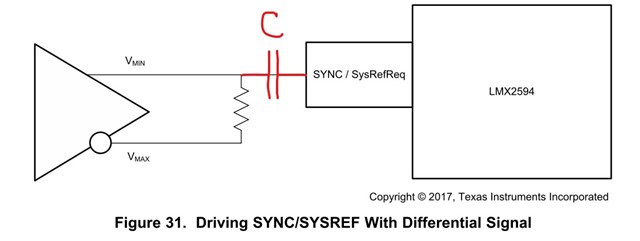

它可能与 LMX2594类似、具有额外的交流耦合电容器?

(我随附 了基于 LMX2594数据表的屏幕截图)

提前感谢您、Alexander。