Other Parts Discussed in Thread: LMK5C33216EVM, LMK5C33216

主题中讨论的其他器件: LMK5C33216

尊敬的所有人:

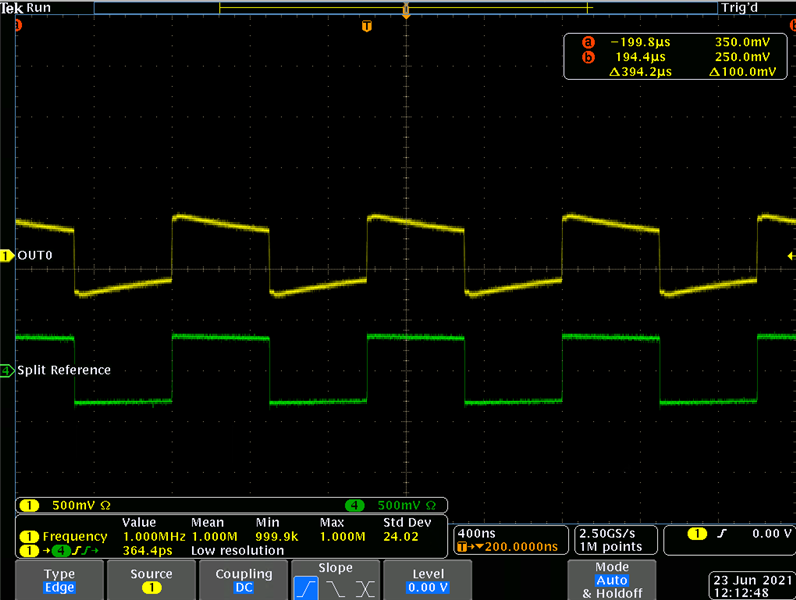

我们尝试在零延迟模式下使用 LMK5C33216EVM、并使用 DPLLx_PH_OFFSET 通过定义的延迟来移动输出。 在第一个测试场景中、我在 REF0上使用10MHz 时钟、并通过 APLL1在 OUT0上生成10MHz 输出。

我的问题/意见是:

1.在哪里可以获得有关如何计算和选择正确的 ZDM 设置参数的详细信息? 数据表、EVM 手册和编程指南对我没有实际帮助。 例如、在第9.3.8.1节中、数据表指出、ZDM 对 VCO 计算有影响、但不会影响如何处理 VCO 以及它是否包含在 TICS PRO 中。

2.最小和最大可变延迟有多大,如何计算(假设这些数字取决于 VCO 频率)?

3.如何访问 DPLLx_PH_OFFSET 寄存器? 仅通过 TICS PRO SW 中的原始寄存器?

4.如果我尝试在 DPLL1-Window 中使用按钮'run script',软件会返回一个 python 错误:'REF0_FREQ is not defined'(但是,它已定义)。

5. TicsPro 何时支持 ZDM 功能?

6.我使用 Si5338作为参考输入。 它满足了第7.5节中相应的所有要求、但我得到了 RFX_MISSCLK_STATUS 事件的列表。 即使在验证页面中将限制设置为最大值、也不会改善行为。 另一方面、即使我将基准设置为11MHz (而不是10MHz)、情况也不会变得更糟。 因此、我必须禁用缺少时钟窗口检测器。 这是否会导致 DPLL 不锁相(LOPL_DPLL1已设置)?

请提供建议吗?

此致、Thorsten