你(们)好。

我的客户现在在其项目中使用04828。

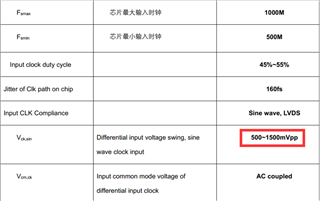

将输出设置为 LVPECL 模式后、将其连接到两个并行通道的 ADC 差分输入(1至2)、且时钟振幅仅为200mV。 它非常低。 当它为1:1时、它仅约为400mV。 我们下游 ADC 通道的单通道时钟需要至少500mV 或更高的电压。

硬件已经被调试了多种外设阻抗匹配参数、但是这些参数没有被改进。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Amelie:

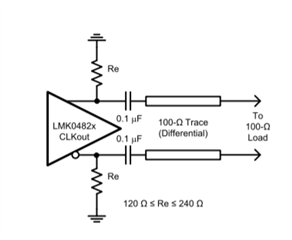

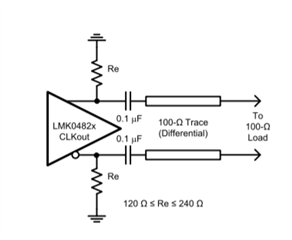

LMK04828 LVPECL 输出格式基于输出频率支持更多 VOD 电压、因此需要输出终端来实现这一点。

有关 LVPECL 输出终端、请参阅 LMK04828数据表中的第10.4.1节。

我知道、客户所需的最大工作频率为1000MHz、LVPECL 在该频率下的振幅应高于客户测量的频率。

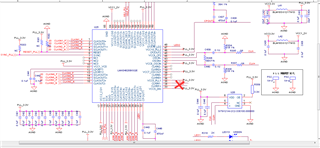

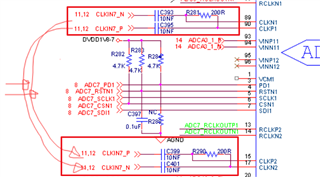

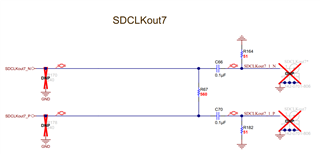

由于原理图图像不是很清楚/不够大、无法在 LMK04828的 CLKin7输出端看到 LVPECL 端接。 在提供足够的终止后、客户应达到所需的时钟振幅。

此致、

Ajeet Pal

您好、Ajeet、

感谢您的回复。

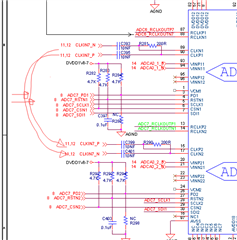

LMK04828的 CLKin7输出端的 LVPECL 端接如下:

1:2、每个都有2个10nF 电容和200 Ω 分辨率。 是角架。

我们有两个问题:

EVM 和 数据表不同。

为什么有时 RES 位于电容器前面、有时电容器位于电容器前面?

如果客户使用1:2、什么是上限和下限值、请在分辨率前使用上限?

EVM:

数据表:

2.如何测量该 CLKout 的波形?

客户没有差分探头; 他们是否可以 使用 两 个单端探头 和两 个示波器通道(High-Z) 进行减法 来测量波形?

尊敬的 Amelie:

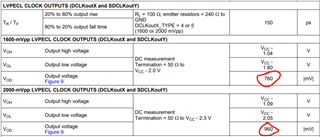

提供的端接 对 LVPECL 输出不起作用。 LVPECL 输出电压和 CM 由正确的终端定义。 如数据表中建议的那样、它要求端接电阻介于120ohm 至240ohm 之间、这相当于 50 ohm 端接电阻与 Vcc - 2V

[引用 userid="377196" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1012656/lmk04828-the-clock-amplitude-is-low/3743269 #3743269"]EVM 和 数据表不同。

为什么有时 RES 位于电容器前面、有时电容器位于电容器前面?

如果客户使用1:2、什么是上限和下限值、请在分辨率前使用上限?

[/报价]LMK04828 EVM 旨在实现电路板的所有可能输出、但每个通道输出都是硬件配置的独立输出格式。 例如、DCLKout0/2和 SDCLKout1/3为 LVPECL 输出配置为硬件、而 DCLKout10和 SDCLKout11为 LVDS。 对于 LVDS、所有其他通道的端接电阻为50欧姆、作为板载负载。

客户至少 可以在提供正确端接后尝试使用单通道并查看振幅电平、但它可能会对其他通道产生一些残桩效应、需要正确端接该通道。

在加载2个通道时、它会影响 LVPECL 输出的整体振幅、并且无法保证提供相同的振幅电平。

[引用 userid="377196" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1012656/lmk04828-the-clock-amplitude-is-low/3743269 #3743269"]2.如何测量该 CLKout 的波形?

客户没有差分探头; 他们是否可以 使用 两 个单端探头 和两 个示波器通道(High-Z) 进行减法 来测量波形?

[/报价]

校正 LVPECL 输出端接后 、LMK 应生成足够的输出功率水平、并可使用示波器上的单端高频探针对其进行探测。

此致、

Ajeet Pal