您好!

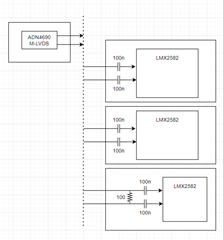

我的设计中希望使用 LMX2582生成~3.6GHz 本地时钟。 LMX2582的唯一时钟基准来自背板上提供的高保真10MHz 时钟、使用 M-LVDS 分配此参考时钟。

我计划将 LMX2582用于此背板上的三个插卡中的每一个。

我有2个问题:

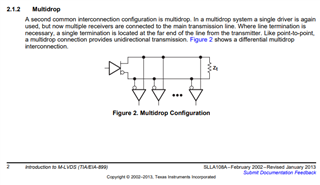

在每个 LMX2582输入端接此多点 LVDS 时钟的最佳方式是什么? 如果没有必要、我更愿意使用 LVDS 接收器芯片。

2.不建议为 LMX2582使用此类低频时钟基准? 如果是、建议使用哪些选项来升高此高频10MHz 基准?

谢谢、

Josh