Other Parts Discussed in Thread: LMK04208EVM, LMK04208

主题中讨论的其他器件: LMK04208

您好!

我们希望用76.8MHz 替换此电路板上的 VCXO。 请为此提供 TI 建议的正确器件型号。 我们目前有122.88 VCXO 板载。

谢谢、

Syahriza Andiko

英特尔公司

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMK04208EVM, LMK04208

您好!

我们希望用76.8MHz 替换此电路板上的 VCXO。 请为此提供 TI 建议的正确器件型号。 我们目前有122.88 VCXO 板载。

谢谢、

Syahriza Andiko

英特尔公司

您好 Syahriza、

LMK04208EVM 上的封装尺寸应同时支持5x7mm VCXO 和9x14mm VCXO。 对于5x7mm、请考虑 CT 提供的356P/L。对于9x14毫米、请考虑 Crystek CVHD-950-76.800。 如果需要最佳性能、我强烈推荐 Crystek VCXO、因为市场上几乎所有其他 VCXO 的性能都较低(典型值约为500fs)。

此致、

Derek Payne

U2封装位于 U8封装的上方、具有兼容的封装。 需要进行两项更改:

此致、

Derek Payne

OSCin 或 CLKIN 单端有两个关键要求:

鉴于 CVHD-950 76.8M 是 CMOS 振荡器、因此应满足压摆率要求(即使幅度减小)。 6dB 焊盘不会将 CMOS 振幅降低到200mVpp 以下。 我怀疑 VCXO 信号质量不是问题。 另一方面、38.4MHz 信号是否满足 CLKIN 的这些要求? 50Ω 2π 为38.4MHz 的信号发生器正弦波、压摆率可能会太低;正弦波压摆率为 SR =Δ V*f*Vpk、该值大约为+6dBm 至 Δ V、以满足最小压摆率要求。 如果38.4MHz 是方波或 LVDS 等其他标准、则此问题可能不适用。

接下来、您是否已确保 PLL1的环路滤波器在76.8MHz VCXO 中仍然有效? 我们免费提供 PLLatinum Sim 工具、可帮助计算环路滤波器值或检查环路稳定性和相位噪声性能。

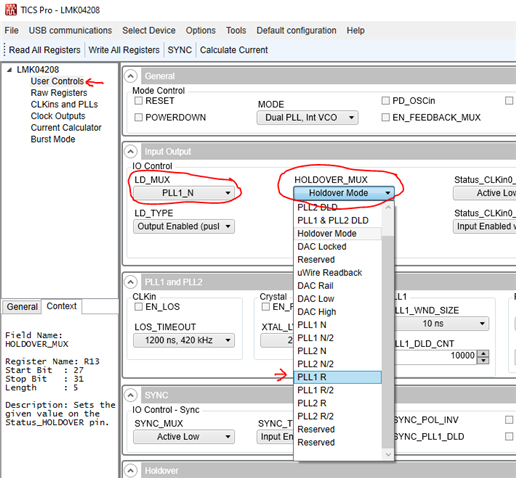

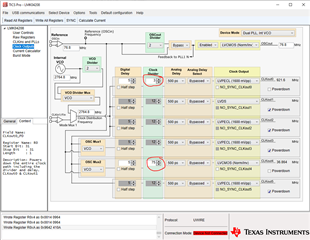

假设没有任何问题、我通常的下一步是切换 I/O 以显示 PLL1 R 和 N 信号、并使用示波器进行检查。 用于切换 I/O 信号的控件是 LD_MUX 和 HOLDDOV_MUX、位于"输入输出"组下的"用户控件"页面中。 检查 PLL 相位检测器输入可以识别未接收到信号的问题:

此致、

Derek Payne

您好 Syahriza、很抱歉耽误您的时间:

CPout1电压可在 VTUNE1_TP 或引脚34处测量(如果您勇敢:)

N 和 R 信号将在上面我建议的方案中的 Status_LD 引脚和 Status_Holdover 引脚上公开。 这些分别在 LD_TP 和 Holdove_TP 中公开。

如果您仍不确定原始值、请参阅《LMK04208EVM 用户指南》的第18页。

此致、

Derek Payne

Syahriza、

如果 VCXO 增益随频率变化(即两个 VCXO 频率的 PPM/V 增益相同)、则环路带宽应保持不变。

我想我没有清楚地解释过这一点:您实际上可以设置 Status_LD 和 Holdove_LD 引脚以显示除锁定检测状态或保持状态之外的信号。 您可以路由出器件的一些信号是 PLL1 R/N 分频器输出端信号的缓冲副本、或者换句话说、是 PLL 相位检测器的输入。 路由分压器输出(即相位检测器输入)有助于诊断您可能看到的一些锁定问题。 我包含了一个下图、以阐明如何配置 Status_LD 和 Holdove_LD 引脚:

此致、

Derek Payne

尊敬的 Derek:

我们将 VCXO 替换为 Crystek CVHD-950-76.800 、并进行了建议的返工。 此外、我们还更换了 PLL1的以下外部环路滤波器组件。

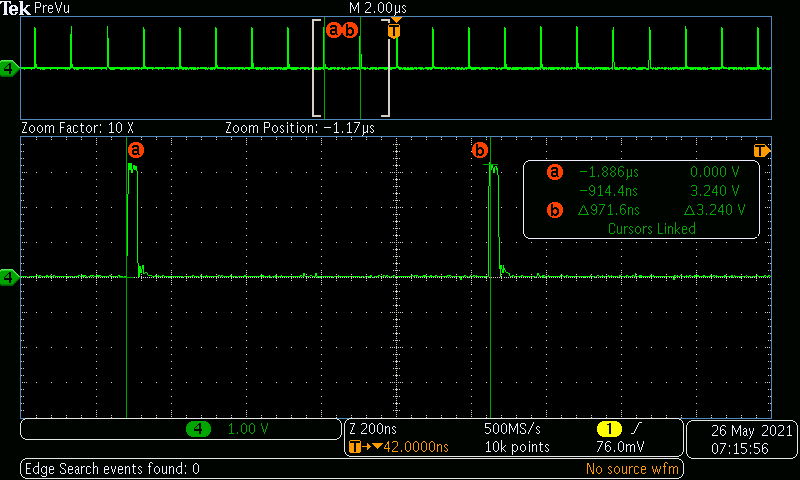

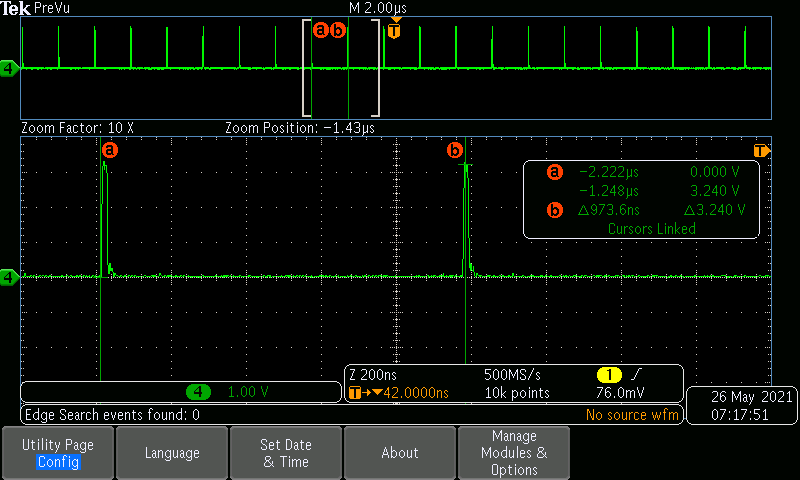

在 CLKIN1上使用频率基准38.4MHz 时、我们不会观察 LD。 (也没有观察到 N 信号(LD_MUX = PLL1 N))

发现 VCXO 已损坏。 替换了损坏的 VCXO、现在我们可以观察 N 和 R 信号、但仍然没有 LD 光。 BTW、我们如何将文件上传到此 TT 中? 。

e2e.ti.com/.../38p4MHz_5F00_RefWith_5F00_VCXO_5F00_76.8_5F00_R_5F00_N.tcs

以下是实施的更改:

1.将122.88MHz VCX0替换为 Crystek CVHD-950-76.800

2. 替换了以下内容:

3. C38移动以填充 C40

151Ω 将 R17/C12/R12转换为6dB 焊盘 à Ω(R17= 151Ω Ω、C12= 37.3Ω Ω、R12=Ω)

在上述所有变化之后、没有观察到 LD 信号(参考频率:38.4MHz)。 请看前面 注释中观察到的 N 和 R 信号以及配置文件。

因此、不确定这里的问题是什么。 有什么意见? 。

Syahriza、

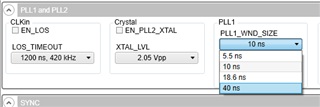

使用此配置、您是否看到 VCXO 引脚上的 Vtune 电压接近1.65V? PLL 可能已锁定、但锁定检测窗口设置得太紧。 如果您看到 Vtune 电压接近1.65V、则可以尝试将 PLL1窗口设置得更宽松一点、时间为40ns:

如果在杂草中 VTune 仍然处于关闭状态、下一步您可以尝试将电荷泵输出电流设置为1.6mA 进行调试吗? 我看到您设置了0.1mA、我想知道是否存在影响电流的 VCXO 输入阻抗或泄漏问题... 0.1mA 不是那么大的电流、因此有时它的驱动强度不够。 另一种可能是、降低的10Hz 环路带宽不会跟踪其他一些噪声源、例如来自某些系统电源的60Hz 线路噪声。 我检查了 PLLatinum Sim 和 PLL1在电荷泵电流较高时仍应保持稳定。

此致、

Derek Payne

谢谢 Derek。

Vtune 大约为1.8伏。 它比预期的略高。

将 PLL1窗口更改为40ns、也将电荷泵电流更改为1.6mA。 VTune 或 LD 中没有变化

我们看到的另一个问题是 CLock4输出不准确、使用电流设置(已连接)e2e.ti.com/.../38p4MHz_5F00_RefWith_5F00_VCXO_5F00_76.8_5F00_0526.tcs 时、ClockOut4的输出应为76.8MHz、测量值为105.98MHz

您好 Syahriza、

很抱歉耽误您的时间、E2E 决定隐藏我的"回复"按钮...

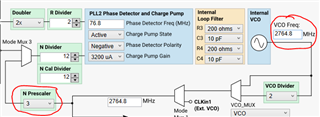

我看到 VCO 配置为1843.2MHz、但您使用的是内部 VCO。 LMK04208的 VCO 频率范围为2750MHz 至3072MHz。 您是否打算将 N 预分频器设置为3、时钟输出分频器提高50%?

此外、在用户控件中、我看到您有 PLL2_FAST_PDF=1。 对于小于100MHz 的相位检测器频率、应将其设置为0。

此致、

Derek Payne